炒股就看金麒麟分析师研报,权威,专业,及时,全面,助您挖掘潜力主题机会!

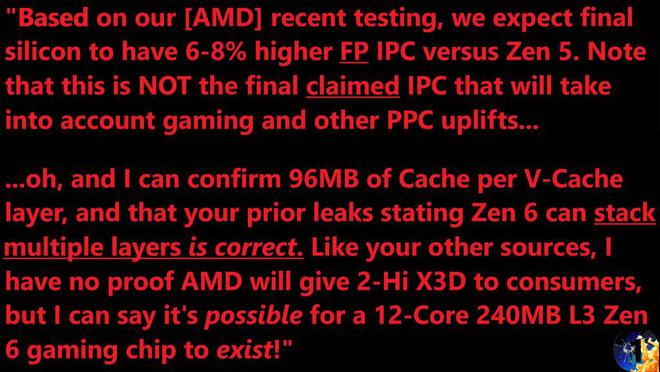

IT之家 7 月 4 日消息,消息源 Moore's Law Is Dead(MLID)在最新一期视频中,曝料称 AMD 将变革 Zen 6 架构,通过多层 3D 堆叠缓存,相比较 Zen 5 架构,FP IPC (浮点运算每时钟指令数) 增幅可达到 6~8%。

在 Zen 5 架构上,每个 3D V-Cache 层最高可以缓存 64MB,而在 Zen 6 架构上,增加到 96MB。

IT之家援引博文介绍,此外 AMD 还计划重新设计芯粒(chiplets),每个核心复合芯片(CCD)可以容纳 12 核,意味着消费级桌面和笔记本电脑最多能拥有 24 个核心。

在单 CCD Ryzen 处理器上,由于 CCD 包含 48MB(每个核心 4MB)和一层 3D V-Cache(96MB)计算,其 L3 缓存可以达到 144MB(48+96)。

如果按照堆叠双 3D V-Cache 计算,那么 L3 缓存最高可以达到 240MB(96 + 96 + 48)。此外,Zen 6 架构还预计将带来更高的核心频率和更多的核心数量,结合先进的台积电制程工艺,这将使其在性能上更具竞争力。

海量资讯、精准解读,尽在新浪财经APP