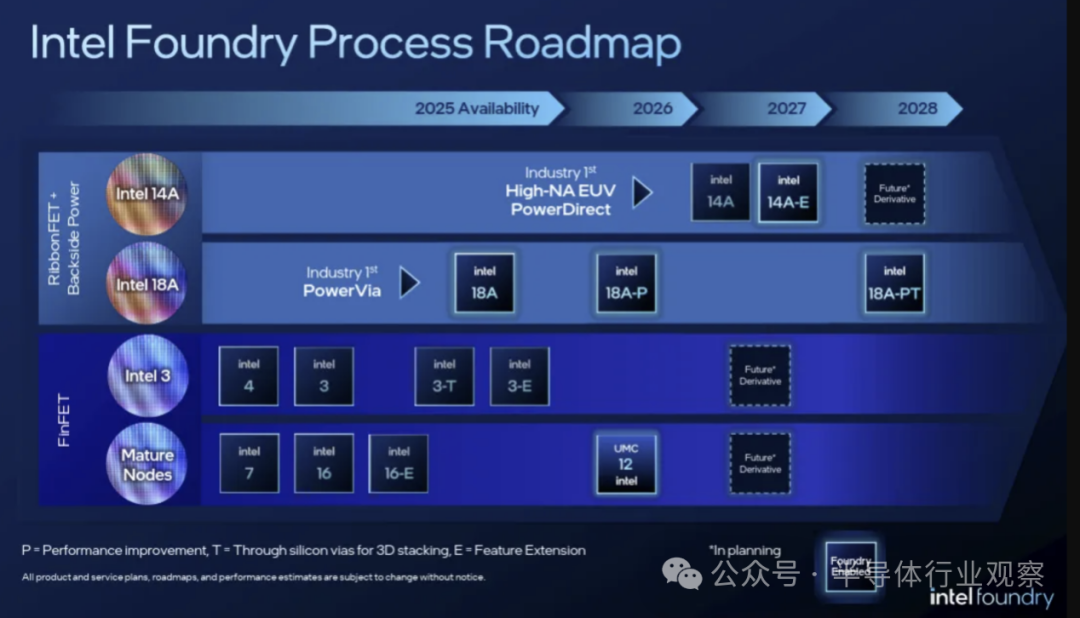

英特爾舉辦了晶圓代工大會,會上公司指出,正在與主要客戶洽談即將推出的14A工藝節點(相當於1.4納米),該節點是18A工藝節點的後續產品。英特爾已有多家客戶計劃流片14A測試芯片。英特爾還透露,公司至關重要的18A節點目前已進入風險生產階段,並計劃於今年晚些時候實現量產。

英特爾新的18A-P擴展節點(18A節點的高性能變體)目前正在晶圓廠早期生產。此外,該公司正在開發一種新的18A-PT變體,該變體支持帶有混合鍵合互連的Foveros Direct 3D,使該公司能夠在其最先進的前沿節點上垂直堆疊芯片。

在英特爾的新方案中,Foveros Direct 3D 技術是一項關鍵的進展,因為它提供了競爭對手台積電(TSMC)已在生產中使用的功能,最著名的是 AMD 的 3D V-Cache 產品。事實上,英特爾的實現在關鍵互連密度測量方面與台積電的產品不相上下。

在成熟節點方面,英特爾代工廠目前已在晶圓廠中完成其首個 16nm 生產流片,並且該公司目前還在與聯華電子合作開發的 12nm 節點吸引客戶。

接下來,我們來看一下這家巨頭的晶圓代工最新路線圖。

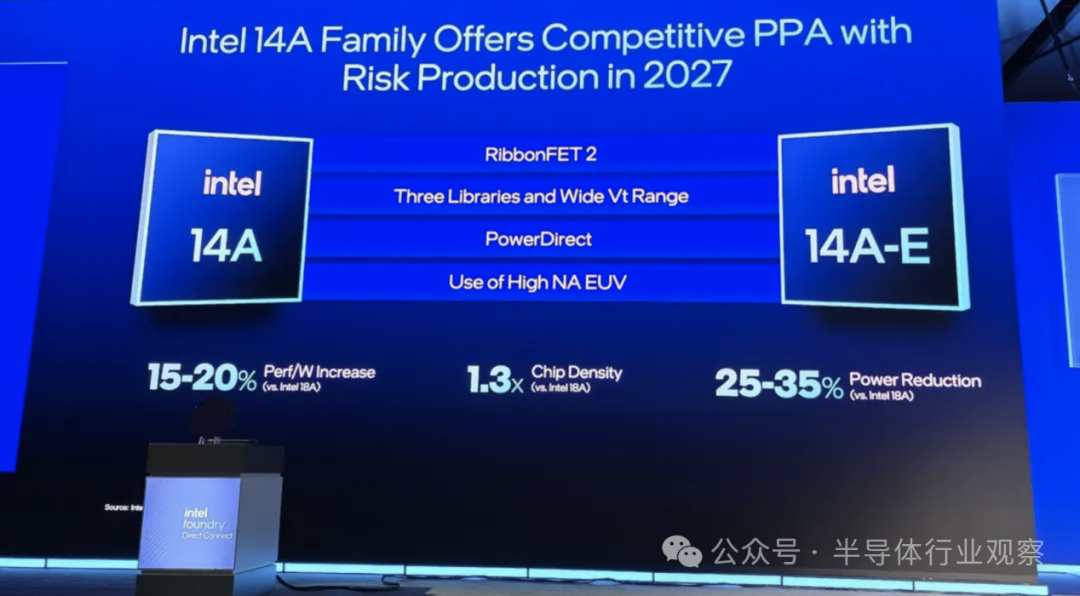

英特爾 14A 工藝節點

英特爾的 14A 是繼 18A 之後的下一代產品,目前已在開發中,但該公司尚未公布具體的時間表。如果一切順利,14A 將成為業界首個採用高數值孔徑 EUV 光刻技術的節點。台積電的競爭對手 A14(1.4 納米級)節點預計將於 2028 年問世,但這家台灣公司不會在生產中使用高數值孔徑 EUV 光刻技術。

英特爾已經與其主要的 14A 工藝節點客戶共享了工藝設計套件 (PDK) 的早期版本,該套件包含一套數據、文檔和設計規則,可用於設計和驗證處理器設計。英特爾表示,已有多家客戶表示有意使用 14A 工藝節點製造芯片。

英特爾的 14A 將採用其 PowerVia 背面供電技術的第二代版本。新的 PowerDirect 方案是一種更先進、更復雜的方案,它通過專門的觸點將電源直接傳輸到每個晶體管的源極和漏極,從而最大限度地降低電阻並提高電源效率。與英特爾目前的 PowerVia 方案(通過納米硅通孔 (Nano TSV) 連接到晶體管的觸點層)相比,這是一種更直接、更高效的連接。

台積電的 N2 節點不包含背面供電;然而,A16將採用直接接觸式背面供電網絡,稱為超級電源軌 (SPR)。A16 本質上是 N2P 節點的衍生產品,並帶有 SPR 技術。A16 節點預計將於 2026 年底投入生產。台積電的 A14 不會採用背面供電設計方法。

英特爾表示,14A 工藝將引入新的「turbo cell」技術,旨在進一步提高芯片的速度,「包括 CPU 最大頻率和 GPU 關鍵路徑」 。

英特爾在一份聲明中表示:「Turbo Cells 允許設計人員在設計模塊內優化性能更高的單元和更節能的單元的組合,從而針對目標應用實現功耗、性能和麪積之間的平衡。」

英特爾強調,公司已經有第二台High NA EUV設備在intel 14A上投入運行。這台設備比第一台設備啓動速度快得多。

英特爾總結說:14A工藝採用 PowerDirect 與 RibbonFET 2 相結合,具備以下優勢:

1、PowerDirect,我們的第二代背面供電網絡。

2、RibbonFET 2,我們的第二代環繞柵極技術。

3、我們推出的 Turbo Cells 是增強型單元技術,與 RibbonFET 2 配合使用時可進一步提高速度(包括 CPU 最大頻率和 GPU 關鍵路徑)。Turbo Cells 允許設計人員在設計模塊內優化性能更高的單元和更節能的單元組合,從而針對目標應用實現功耗、性能和麪積之間的平衡。

4、業界首款高數值孔徑 (High NA) EUV,可實現較小工藝特徵的經濟高效打印。

英特爾的路線圖還補充道,14A 工藝將於 2027 年問世,同時還將開發一個「14A-E」節點,以包含一些額外的「功能擴展」。

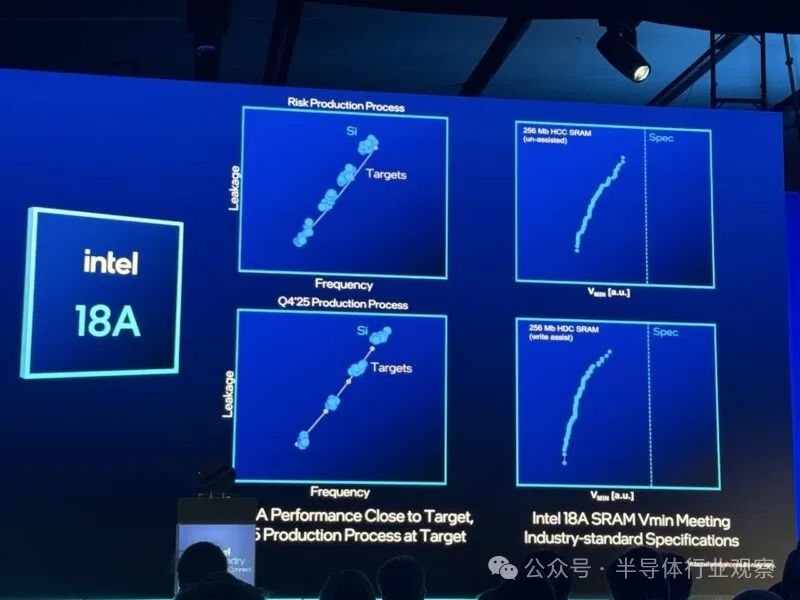

英特爾 18A 工藝節點更新

正如我們上個月報道的那樣,英特爾的 18A(1.8 納米等效)工藝節點已進入風險生產階段,標誌着該節點的首批小批量生產正式啓動,大批量生產 (HVM) 計劃於年底啓動。英特爾並未具體說明哪些處理器已開始生產,但具體時間與其 Panther Lake 處理器的預期基本一致,後者預計將於年底上市。英特爾首批 18A 工藝節點將在其俄勒岡州的晶圓廠生產,但該公司已在其亞利桑那州的晶圓廠「運行 18A 批次」,這表明該工廠也將很快開始生產。

18A 節點是業界首個同時採用PowerVia 背面供電網絡 (BSPDN)和RibbonFET 環柵 (GAA) 晶體管的產品化節點。PowerVia 在芯片背面提供優化的電源佈線,以提高性能和晶體管密度。RibbonFET 還通過使用完全被柵極包圍的四個垂直納米片,在更小的面積內提供更高的晶體管密度和更快的晶體管開關速度。

18A 節點進入 HVM 的時間與台積電的競爭對手 2nm N2 節點大致相同。然而,台積電的 N2 節點沒有配備背面供電網絡 (PSN),但它採用了具有三個垂直納米片的 GAA 技術。根據最近一次行業活動的演示,人們對這兩個工藝節點進行了一些基本的比較。總體來看,英特爾的節點比台積電更快、功耗更低,儘管台積電在密度(大概還有成本)方面仍佔據優勢。然而,這些區別可能會因不同芯片設計中的具體實現而異。

Panther Lake 將成為英特爾 18A 的首發產品,計劃於 2025 年推出。Clearwater Forest已推遲至 2026 年。外媒還注意到,有客戶正在談論與英特爾 18A 的合作。例如,Trusted Semiconductor Solutions 更專注於國防工業,而不是消費和數據中心領域。

關於Intel 18A,英特爾總結說:

1、與intel 3 工藝節點相比,每瓦性能提高 15%,芯片密度提高 30%;

2、北美最早製造的亞2納米先進節點,為客戶提供有彈性的供應替代方案;

3、業界首創的 PowerVia 背面供電技術,將密度和單元利用率提高 5% 至 10%,並降低電阻供電下降,從而使 ISO 功率性能提高高達 4%,並且與正面功率設計相比,固有電阻 (IR) 下降大大降低。;

4、RibbonFET 環柵 (GAA) 晶體管技術,可實現電流的精確控制。RibbonFET 可進一步縮小芯片元件體積,同時降低功耗,這對於日益密集的芯片而言至關重要;

5、Omni MIM 電容器,顯著降低電感功率下降,增強芯片運行穩定性。此功能對於生成式 AI 等需要突發且高強度計算能力的現代工作負載至關重要;

6、業界標準 EDA 工具和參考流程全面支持,可從其他技術節點平穩過渡。藉助 EDA 合作伙伴提供的參考流程,我們的客戶可以先於其他背面電源解決方案開始使用 PowerVia 進行設計;

7、由 35 多個行業領先的生態系統合作伙伴組成的強大聯盟,涵蓋 EDA、IP、設計服務、雲服務以及航空航天和國防領域,有助於確保廣泛的客戶支持,從而進一步簡化採用;

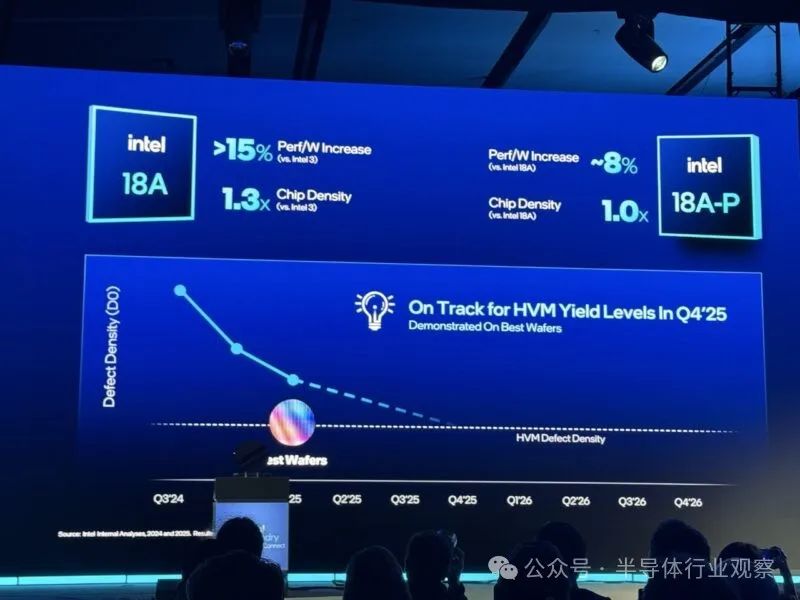

英特爾 18A 家族繼續擴展

英特爾的 18A 節點是主流版本,但該公司也提供了該節點的多個「產品線擴展」,並以不同的後綴命名。這些底層節點的版本針對不同的用例進行了定製。

其中,英特爾 18A-P基於英特爾RibbonFET和PowerVia技術的二次實現,提供新一代性能和更高的能效。它採用新的更低閾值電壓和漏電優化器件,以及新的細晶粒帶寬度,顯著提升了每瓦性能和晶體管性能,同時確保了設計規則的兼容性。

英特爾今日透露,其高性能 18A-P 節點晶圓已在晶圓廠投產。該 18A 節點擁有優化的功率和頻率曲線,每瓦性能提升 5-10%。根據芯片的具體調整,這可以在相同性能下實現更高的時鐘速度或更低的功耗。

18A-P節點的設計規則與18A節點兼容,從而簡化了客戶的設計流程。英特爾已與電子設計自動化 (EDA) 軟件供應商合作,以提供對行業標準設計工具的廣泛支持,同時還與知識產權 (IP) 設計人員合作,提供必要的 IP 模塊,從而簡化實施。

至於英特爾 18A-PT ,則是公司專為構建下一代 3DIC 設計的 AI 和 HPC 客戶而設計,充分利用了英特爾 18A-P 在性能和能效方面的提升。英特爾 18A-PT 採用更新的後端金屬堆棧、直通硅通孔 (TSV)、芯片間硅通孔 (Die-to-Die TSV),以及業界領先間距的先進混合鍵合接口 (HBI),為高級工作負載提供無與倫比的可擴展性和集成度,助力客戶突破 AI 和高性能計算的界限。

據介紹,新的 18A-PT 節點將提供與性能導向的 18A-P 相同的性能和效率優勢,但增加了 Foveros Direct 3D 混合鍵合。這種無凸塊銅對銅鍵合技術(意味着它不使用微凸塊或焊料來連接兩個芯片)將芯片與硅通孔 (TSV) 融合在一起。英特爾的實施方案將採用小於 5 微米的間距,這比其到 2023 年實現 10 微米間距的初始目標有了明顯的改進,以將芯片融合在 18A-PT 芯片的頂部。間距是互連之間中心到中心間距的度量,值越低表示密度越高,越好。

值得注意的是,AMD 使用台積電的 SoIC-X 技術(一種類似的混合鍵合方法)將L3 芯片與其 X3D 處理器上的 9 微米凸點間距進行融合。台積電的 SOIC-X 技術目前範圍從 4.5 微米到 9 微米,但該公司在 2027 年的發展規劃中已提供 3 微米間距的產品。如果能夠按計劃有效實現產品化,英特爾的 Foveros Direct 3D 將顯著提升其相對於台積電封裝技術的定位。

英特爾的 Clearwater Forest 將是其首款採用 Foveros Direct 3D 封裝的產品,但該公司尚未透露該產品的具體規格。值得注意的是,TSV 通常僅包含在基礎芯片中,而 Clearwater Forest 使用英特爾 3-T 作為基礎芯片,並在其上堆疊英特爾 18A 計算芯片。因此,為 18A 啓用 TSV 將允許其在頂部堆疊芯片,而 SRAM 緩存是一個合理的用例。

成熟節點:16nm 和 12nm 繼續推進

英特爾代工廠不僅致力於尖端技術,還在多個成熟節點上開展工作。英特爾的 16nm 節點本質上是其 22FFL 節點的一個版本,利用了行業標準設計工具和 PDK,目前已在晶圓廠完成流片。據英特爾介紹,Intel 16是通往 FinFET 的理想途徑。

此外,英特爾還將繼續與合作伙伴聯華電子合作開發 12nm 節點,該節點將於 2027 年開始在英特爾位於亞利桑那州的三家晶圓廠生產。事實上,英特爾目前正在為該節點尋找主要客戶。12nm 將主要用於移動通信基礎設施和網絡應用。

英特爾總結說,關於16nm,市公司通過創新合作擴大的產品組合:

1、UMC 和英特爾代工廠正在合作開發 12nm 技術平台,將英特爾的 FinFET 專業知識與 UMC 的邏輯和混合模式/RF 經驗結合在一起;

2、與業界 12nm 具有競爭力;

3、通過訪問地理分佈更加多樣化、更具彈性的供應鏈,為客戶提供更多的採購決策選擇;

4、非常適合移動、無線連接和網絡應用等高增長市場;

英特爾的先進封裝規劃

英特爾的先進封裝服務也尤為重要,因為它們能夠以最快的速度實現顯著的創收。Intle 也的確討論了其在新墨西哥州和馬來西亞等地談論其先進的封裝解決方案。

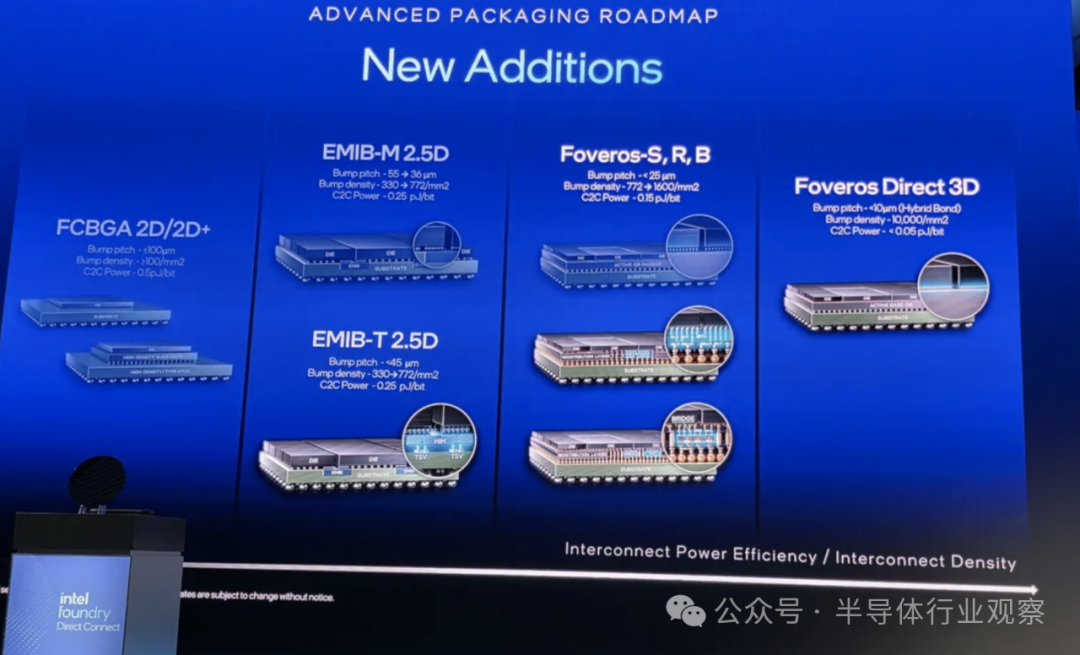

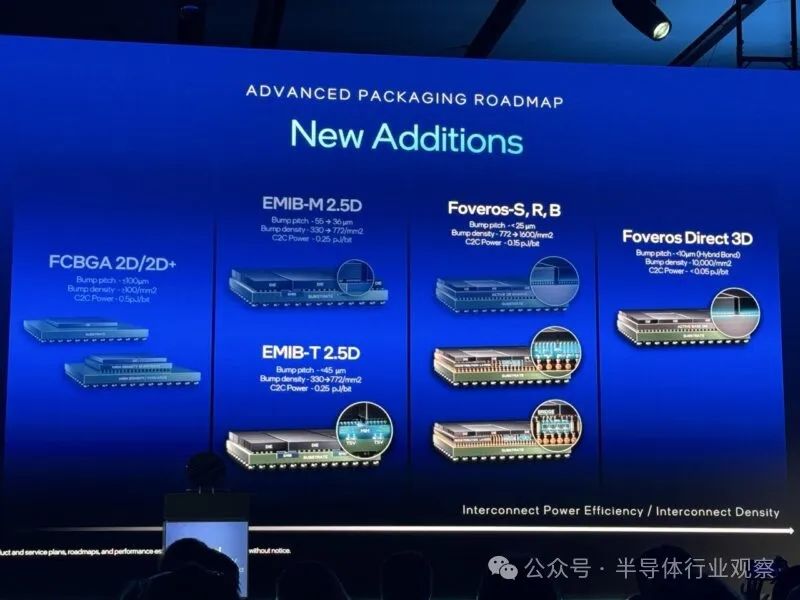

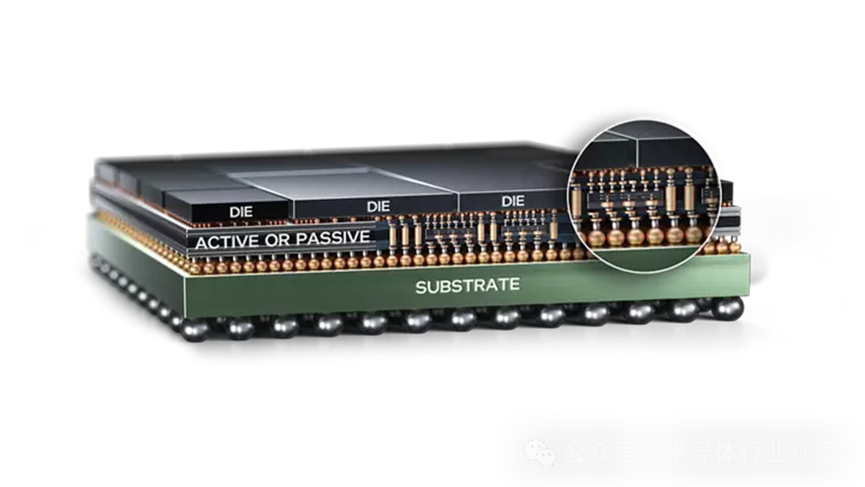

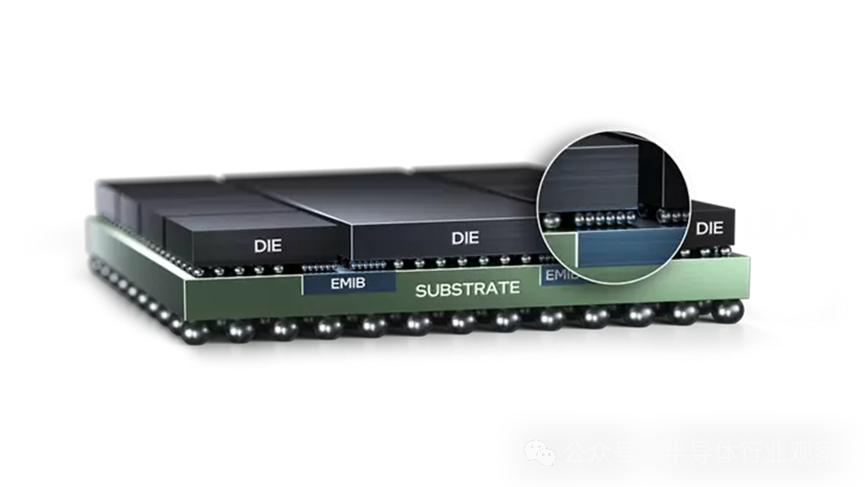

但英特爾還在持續更新其封裝路線圖,例如用於 EMIB-T 的 TSV 和 EMIB,以及新的低成本 Foveros。

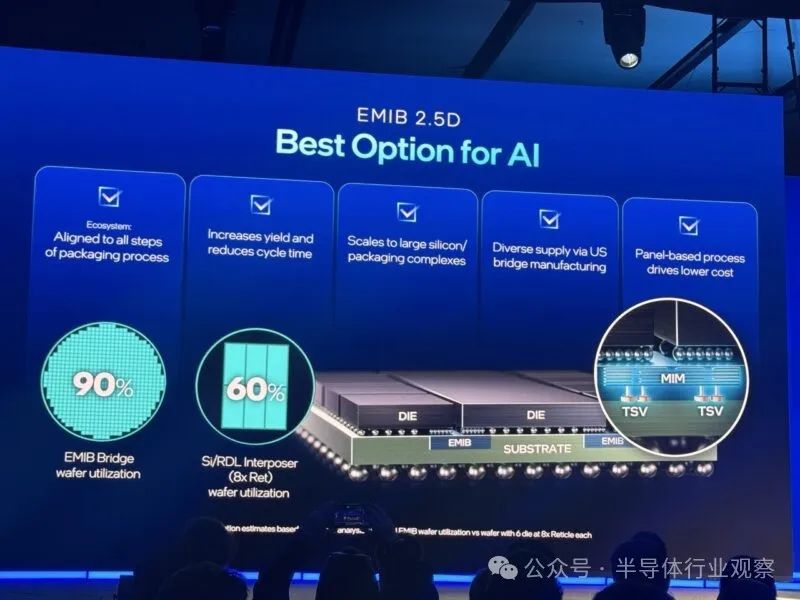

英特爾正在討論使用 EMIB 2.5D 來替代大型硅中介層,因為它可以將製造時間縮短數周。

英特爾還在討論更多共封裝光學器件。

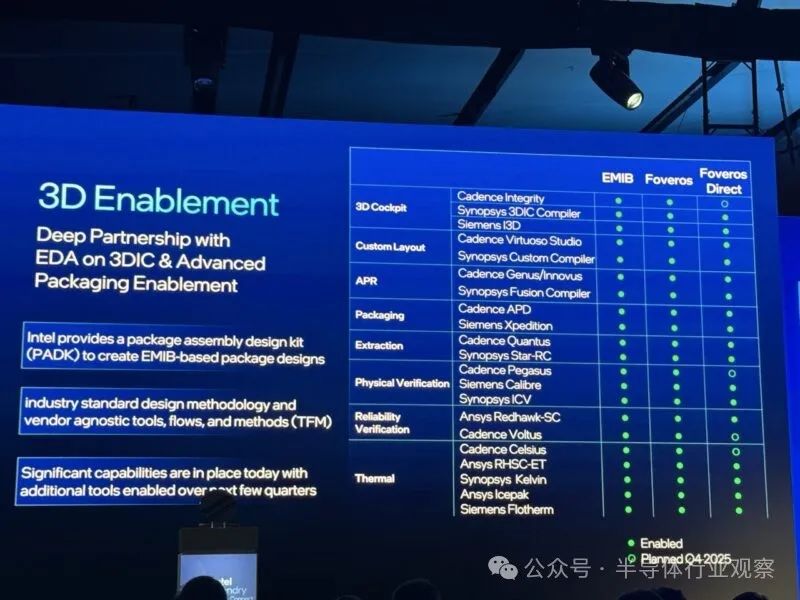

關於3D封裝,英特爾也提供瞭如下的支持:

英特爾邀請安靠公司(Amkor)登台,討論如何為合作伙伴提供EMIB。安靠公司表示,將把先進封裝技術引入亞利桑那州,以增強其現有的韓國和葡萄牙工廠。

在新聞稿中,英特爾強調,英特爾代工廠提供多種配置。芯片可以通過英特爾代工廠高級系統組裝與測試 (Intel Foundry ASAT) 或外包半導體組裝與測試 (OSAT) 進行製造。然後,芯片通過優化的互連技術進行連接,我們助力推動行業標準,例如通用芯片互連規範 (UCIe)。

英特爾還能幫助您整合前端和後端技術,打造系統級優化的解決方案。此外,我們憑藉強大、地域分佈廣泛且產能強大的製造基地,提供無與倫比的規模和深度的組裝和測試能力。

英特爾總結:

1.公司的代工廠使用英特爾 18A-PT 上的英特爾 14A 提供系統級集成,然後通過 Foveros Direct(3D 堆疊)和嵌入式多芯片互連橋接(2.5D 橋接)進行連接;

2.公司新的先進封裝技術產品包括 EMIB-T,可滿足未來的高帶寬內存需求,以及 Foveros 架構的兩個新功能:Foveros-R 和 Foveros-B,為客戶提供更多高效靈活的選擇;

3.通過與 Amkor Technology 的新合作提高了客戶選擇適合其需求的先進封裝技術的靈活性。

據介紹,Foveros-S 2.5D是應熱吻針對成本/性能進行了優化的下一代封裝,具有以下幾個特點:

1、帶有 4x 標線的硅中介層。

2、適用於客戶端應用程序。

3、非常適合具有多個頂部芯片的解決方案。

4、生產驗證:自 2019 年起採用主動基模進行量產。

Foveros-R 2.5D則採用重分佈層 (RDL) 中介層來創建芯片之間的異構集成。適用於客戶和成本敏感的領域、非常適合需要多個頂部芯片的複雜功能需求的解決方案。按照計劃,該工藝將於2027 年準備投入生產。

Foveros-B 2.5D將電源和信號的重分佈層 (RDL) 與硅橋相結合,為複雜設計提供靈活的解決方案。據介紹,這個工藝適用於客戶端和數據中心應用,非常適合具有多個基本芯片小芯片的解決方案,例如緩存分解、DVR 或 MIM。英特爾表示,這個封裝同樣將於2027 年準備投入生產。

Foveros Direct 3D則是在在有源基片上進行 3D 芯片堆疊,以實現卓越的每比特功率性能。總結而言,該封裝擁有以下幾點優勢:

1、Cu-Cu混合鍵合界面(HBI)。

2、超高帶寬和低功耗互連。

3、高密度、低電阻的芯片間互連。

4、適用於客戶端和數據中心應用。

5、EMIB 3.5D 解決方案上啓用了 Foveros Direct 堆棧。

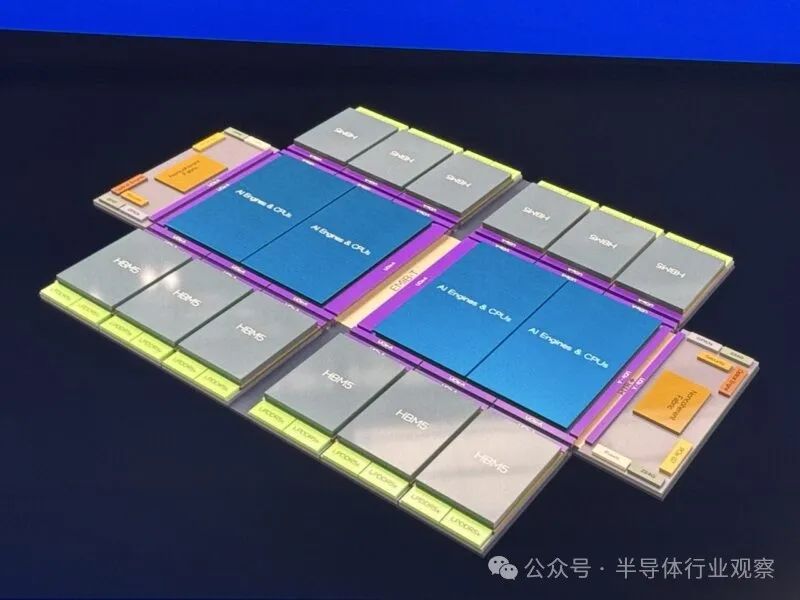

EMIB 3.5D則是在一個封裝中嵌入了多芯片互連橋 3.5D 和 Foveros。

可以實現具有多種模具的靈活異構系統;非常適合需要將多個 3D 堆棧組合在一個包中的應用;英特爾數據中心 GPU Max 系列 SoC:採用 EMIB 3.5D 打造英特爾有史以來量產的最複雜的異構芯片,擁有超過 1000 億個晶體管、47 個活動塊、5 個工藝節點。

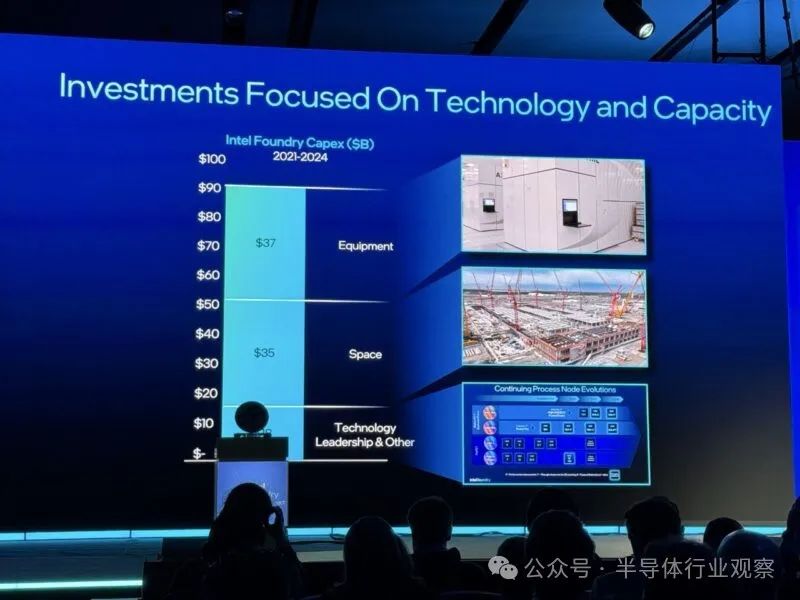

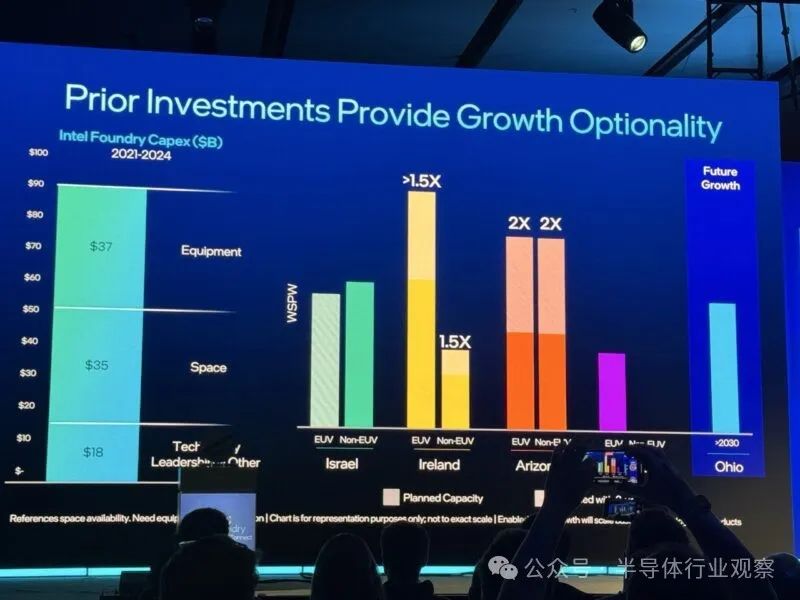

英特爾的製造和產能分享

在演講中,英特爾表示,公司一直在技術和產能方面進行投資。

英特爾在全球擁有多處製造基地。

在以色列和亞利桑那州,英特爾擁有成熟的intel 10 和intel 7。

現在英特爾重點關注亞利桑那州的製造工廠。

英特爾展示了其在各地點的現有產能,同時也展示了其未來增長潛力。英特爾表示,未來6到8個季度,其現有工廠的產能將得以提升。

除了晶圓製造之外,英特爾還擁有封裝能力和發展空間。

更多內容

在大會上,英特爾展示了未來的 12x 光罩芯片,該芯片具有 AI 引擎、高速互連、HBM5 和 LPDDR5x、PCIe Gen7、光學引擎、UCIe-A、EMIB-T、224G PHY、安全塊等。

英特爾還公布了公司代工加速器聯盟(英特爾代工芯片聯盟和價值鏈聯盟)內增加了新的項目,同時還發布了一系列來自頂級生態系統合作伙伴的公告。例如英特爾就帶來了Chiplet聯盟。

英特爾表示,英特爾代工 (Intel Foundry) 擁有全面的知識產權 (IP)、電子設計自動化 (EDA) 和設計服務解決方案組合,這些解決方案由值得信賴且久經考驗的生態系統合作伙伴提供,旨在推動超越傳統節點擴展的進步。

作為英特爾代工加速器聯盟的最新項目,全新的英特爾代工 Chiplet 聯盟將首先專注於定義和推動面向政府應用和關鍵商業市場的先進技術基礎設施。英特爾代工 Chiplet 聯盟將為希望部署利用可互操作且安全的 Chiplet 解決方案針對目標應用和市場的設計的客戶提供一條可靠且可擴展的途徑。

此外,英特爾代工加速器聯盟還包括IP聯盟、EDA聯盟、設計服務聯盟、雲聯盟和USMAG聯盟。

不過,我們也看到,英特爾為了削減成本,取消了20A節點的量產,但目前其18A節點即將量產,這標誌着英特爾在尋求重奪超越台積電的製造領先地位方面邁出了關鍵的一步。新增的生產線擴展,尤其是支持芯片堆疊的18A-PT,是一項尤為顯著的進步,將有助於英特爾進一步提升對潛在代工客戶的吸引力。

英特爾14A工藝節點的開發也進展順利,這意味着該公司正穩步推進路線圖的新節點和新功能的開發。我們尚未聽到有關英特爾10A(1納米級)工藝節點計劃的任何新細節,該節點預計將於2027年開始開發。英特爾的新聞稿中也沒有提及英特爾3節點的任何新進展,但我們預計更多細節將在當天陸續披露。

英特爾此次活動重點展示其廣泛的EDA、IP和服務產品組合,這些產品組合由新思科技和Cadence等行業巨頭的生態系統驅動。新成立的英特爾芯片代工聯盟(Intel Foundry Chiplet Alliance)也是一項重要進展,它將使客戶能夠基於可互操作且經過驗證的設計,將芯片組合搭配到他們的設計中。