文|半導體產業縱橫

先進的封裝技術和Chiplet要求採用精密且靈活的測試策略。

異構集成正在推動半導體行業的創新,但它也增加了芯片設計的複雜性,需要更為複雜的測試需求。自動測試設備(ATE)行業正在做出響應,開發和使用更精密的測試設備,這些設備能夠處理測試異構芯片所需的多樣功能和接口。這包括測試不同的通信協議、功率域和熱特性,最終使每套集成組件都有自己的參數和性能標準。

異構集成概覽

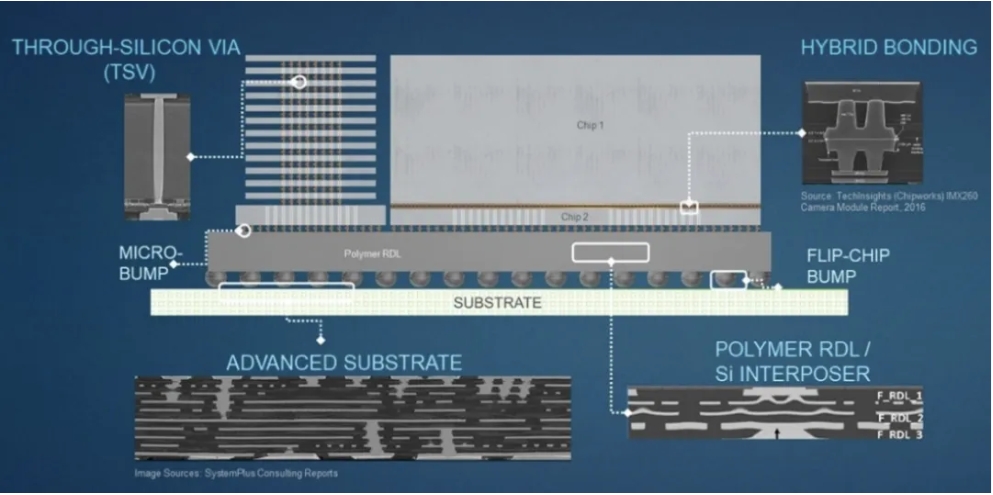

異構芯片,也稱為異構集成,涉及將多個單獨製造的組件(如處理器、存儲器、傳感器)組合成一個封裝體或系統級封裝(SiP)。以這種方式組合的組件,即Chiplet,可以使用不同的工藝和材料製成。圖1展示了異構集成的一個版本。

圖1:異構集成的一個版本。(來源:應用材料公司)

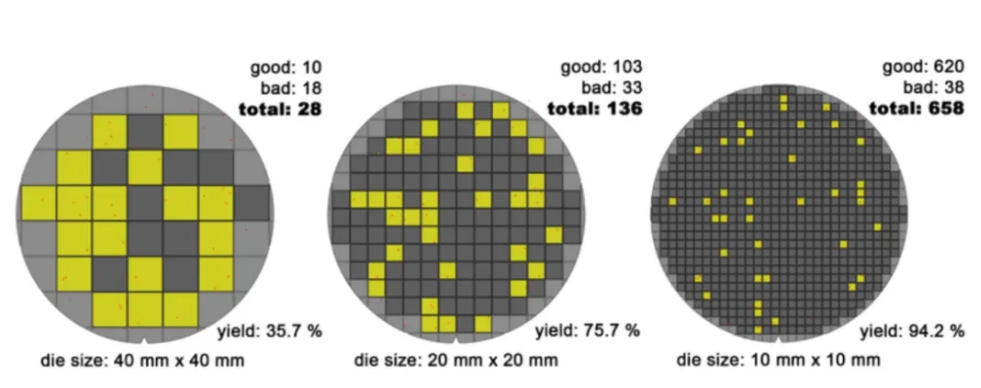

與傳統的同質芯片相比,通過利用各種技術和材料,製造商創造出的 SiP 能更高效地執行多種計算任務。系統設計人員可以在更小的空間內獲得更高的性能、更低的功耗和更強大的功能。同時,與單片設備相比,Chiplet尺寸更小,可大大提高良品率,從而降低相同設備缺陷密度下的成本,如圖 2 所示。這對於AI、5G和IoT等高級應用至關重要,這些應用必須在嚴格的功耗和空間限制內滿足多樣化和密集的計算需求。

圖2:Chiplet相對於單片設備的較小尺寸使其具有更高的良率。(來源:維基共享資源)

隨着技術的不斷進步,幾乎所有設備都可以根據不同的應用組合成異構封裝。因此,測試資源必須能夠測試幾乎所有類型的功能,同時考慮到從低端到高端的經濟性。

對測試行業的全面影響

由於這種增加的複雜性——包括需要更先進的測試設備(如泰瑞達公司的UltraFLEXplus)以及潛在的測試時間延長——優化質量成本至關重要。然而,不同組件之間可能存在相互作用,確保異構芯片的可靠性更具挑戰性。

良率管理也變得更加複雜,因為任何組件中的缺陷都可能影響芯片的整體功能。靈活的測試解決方案可能包括專門的測試算法和夾具,以準確評估每個獨特芯片的性能和可靠性。

靈活的測試策略必不可少

為了適應先進數字芯片和異構集成的複雜性,行業正在進行一系列測試策略。動態測試覆蓋結合了ATE和系統級測試(SLT),在模擬最終使用環境的條件下評估半導體器件。泰瑞達公司的Titan SLT平台就是一個例子,它在需要最高水平系統性能測試的半導體測試環境中提供了靈活性、可擴展性和密度。通過模擬真實世界的場景,動態測試覆蓋範圍可有效識別故障,否則這些故障可能會被隱藏起來。平衡測試成本和改進故障檢測這一策略有助於優化質量成本。此外,它還使製造商能夠利用數據分析提高產量,確保只有最高質量的產品進入市場。

左移和右移策略進一步平衡了整個製造流程中的測試覆蓋。「左移」策略將測試提前到開發過程的早期,通過更早地發現和解決缺陷來降低整體成本。相反,「右移」策略將測試擴展到後期階段,包括製造後測試,確保任何潛在缺陷在到達消費者之前都被發現。這些策略共同優化成本、質量和良率。

測試複雜性帶來挑戰

在2.5D/3D封裝中測試已知良好晶粒(KGD)和已知良好中介層(KGI)存在許多必須考慮的挑戰。集成是複雜的,3D堆疊中的晶粒和中介層導致多層互連和不同的功能。由於硅通孔(TSV)等錯綜複雜的連接以及測試探針物理空間的減少,這些元件的小型化增加了難度。

晶粒內的缺陷可能只有在組件集成後才顯現。堆疊和鍵合過程本身可能會引入新的缺陷或加劇現有缺陷,這是由於熱應力和機械應力造成的。一旦組件堆疊起來,訪問每層進行測試就變得更加困難,需要先進的探測技術和測試訪問機制。

高速互連(包括TSV結構)進一步增加了測試的複雜性。TSV(硅通孔)在硅芯片內部提供垂直連接,對於高密度、高性能封裝至關重要。然而,其複雜的特性在信號完整性、熱管理、製造可變性和測試可訪問性方面帶來了重大挑戰,從而使測試工作變得更加困難。必須對測試設計(DFT)方法進行調整,以適應三維封裝測試的特殊要求,確保徹底覆蓋故障並最大限度地減少測試逃逸。通過採用內置自測試 (BIST) 結構、擴展邊界掃描技術、實施熱感知測試、確保缺陷容限以及採用分層測試方法,製造商可以提高先進3D半導體封裝的可靠性和性能。

泰瑞達遵循IEEE 1838標準來應對這些挑戰,利用其在3D堆疊集成電路中的測試訪問架構綜合框架。IEEE 1838建立了標準化的測試接口和協議,確保來自不同製造商的不同組件可以使用通用框架進行測試。該標準支持模塊化測試訪問架構,能夠在不同層級和組件間實現可擴展且靈活的測試。基於IEEE 1838準則的BIST電路和DFT功能有助於實現更高的故障覆蓋率。為此,泰瑞達的UltraFLEX和UltraFLEXplus以及ETS-88測試儀可為更復雜的器件提供測試能力,提高準確性,降低客戶擁有成本。

展望未來,持續創新

半導體行業在不斷演進,其驅動力來自對更高性能、更高集成度和更低功耗的需求。對半導體測試產生重大影響的新興技術包括行業互連標準,如通用小芯片互連快遞(UCIe),以及共封裝硅光子學的出現。

隨着 UCIe 和硅光子技術的發展,互連變得越來越複雜,因此需要先進的測試方法來確保信號完整性和性能。這包括精確鑑定高速信號和嚴格測試光子元件。

聯合封裝解決方案需要有效的熱管理策略,以防止過熱並確保可靠運行。測試必須考慮熱效應,並採用熱感知測試技術。

隨着這些新興技術的不斷發展,半導體行業將受益於更高的性能、更強的集成能力和更高的能效。然而,測試的複雜性也將增加,這就要求測試方法和設備不斷創新,以應對這些異構系統帶來的獨特挑戰。測試行業要想走在這些趨勢的前面,就要採用標準化的方法和靈活的測試策略確保下一代半導體器件的可靠和高效生產。