最近,蘋果公司新發布了一項名為「具有高動態範圍和低噪點的堆疊像素圖像傳感器」的專利。這項發現可能預示着一項可能重塑移動和專業成像領域的突破。蘋果公司聲稱其堆疊式傳感器架構擁有高達20檔的動態範圍,或許正蓄勢待發,準備與電影攝影機技術領域的巨頭們競爭,甚至超越他們。

一、性能超越最佳的傳感器

蘋果新發布的一項名為「高動態範圍低噪點堆疊像素圖像傳感器」的專利,揭示了成像技術的重大進步。雖然蘋果以其定製芯片和相機軟件而聞名,但這項專利暗示着一項更具雄心的目標:一種完全自主設計的圖像傳感器,其動態範圍有望與領先的電影攝影機相媲美,甚至超越它們。而且,這並非僅僅是理論上的——該傳感器架構聲稱其動態範圍高達120 dB,相當於近20檔的動態範圍。這比目前業界的巨頭,例如ARRI ALEXA 35,都要高得多。

按照蘋果在專利描述文件中所說:

本文描述的本發明實施例提供了一種包含新穎設計的3T像素的圖像傳感器,該傳感器可實現高動態範圍、低噪聲,並且不會出現傳統4T像素陣列中可能出現的僞影。該圖像傳感器包含一個堆疊在邏輯芯片上的傳感器芯片。每個3T像素在傳感器芯片上包含一個傳感電路,該電路包括一個光電二極管和一個橫向溢流積分電容(LOFIC:lateral overflow integration capacitor)電路,以便在從室內到明亮陽光的各種光照條件下進行傳感,而無需自動曝光控制。

此外,每個像素在邏輯芯片上包含一個像素電路,該電路包含一個電流存儲電路。該電流存儲電路用於感測探測器元件中的噪聲水平。電流存儲電路輸出的信號能夠利用CDS抑制熱噪聲(kTC)。

二、蘋果的專利內容是什麼?

該專利概述了一種由兩層組成的堆疊傳感器:傳感器芯片(帶有光電二極管和模擬電路)和邏輯芯片(處理讀出、噪聲消除和控制)。

這種堆疊式方法與索尼的做法類似,使蘋果能夠將先進的電路封裝到更薄的傳感器模塊中,非常適合智能手機和Vision Pro等AR/VR設備。但真正的創新在於像素級架構,其特點如下:

1. LOFIC(橫向溢流積分電容器)

這種機制使傳感器能夠處理三個電荷存儲層級的光溢出,自動適應極端亮度或黑暗環境——一次性完成。這便是20檔動態範圍得以實現的原因。

2. 內置噪聲感應電路

每個像素內的電流存儲電路可實時檢測並消除熱噪聲,這意味着即使在低光照條件下,最終圖像也更加清晰-無需後期處理或AI技巧。

3. 3T像素設計(非4T)

令人驚訝的是,蘋果採用了3晶體管設計,這種設計通常被認為更簡單,但噪音也更大。然而,得益於上述創新,該設計比標準的4T傳感器噪音更低,從而以更少的組件和更高的效率提供更佳的性能。

按照蘋果所說:

本例中的LOFIC電路44包括兩個電荷存儲電容器50和52以及兩個串聯連接到浮動擴散節點42的LOFIC晶體管(LOFIC1和LOFIC2)54和56。第一個LOFIC晶體管(LOFIC1)54將浮動擴散節點連接到第一個電荷存儲電容器50的電荷輸入端,該電容器的電容較小,例如約為20 fF。第二個LOFIC晶體管56將第一個電荷存儲電容器50的電荷輸入端連接到第二個電荷存儲電容器52的電荷輸入端,該電容器的電容較大,例如約為500 fF。

在此配置中,浮動擴散節點42本身將用於在弱光條件下存儲和讀出光電荷;電荷存儲電容器50將用於在中等光照條件下存儲和讀出光電荷;電荷存儲電容器52將用於在強光條件下存儲和讀出光電荷。這種LOFIC結構使探測器元件26能夠感測約120 dB動態範圍內的光。或者,也可以使用其他LOFIC結構,並採用更少或更多數量的電容器和晶體管。

三、這個產品意味着什麼?

如果這項技術得以實施(或許在未來的iPhone 17 Pro或Apple Vision Pro 2中),它可能會導致:

移動設備上的電影級HDR;

實時無噪音視頻捕捉;

超薄外形,專業品質成像,具有極高的DR(20檔動態範圍)。

蘋果可能正準備擺脫對索尼高端相機傳感器的依賴,以競爭對手而非客戶的身份進入圖像傳感器市場。這也表明,蘋果在計算攝影領域的下一次飛躍可能植根於以圖像傳感器為先的創新,而非軟件或人工智能。

動態範圍和噪點是數字成像的兩個主要制約因素。一款能夠提供20檔動態範圍和先進片上噪點抑制功能的移動式或緊湊型傳感器,不僅是一種改進,更是顛覆性的。

這可能會影響:

移動電影攝影;

HDR流媒體內容;

AR/VR視覺保真度;

即使是專業的電影製作套件,緊湊性和質量也必須共存。

由於這是蘋果公司的產品,因此不難想象該公司會將該傳感器與神經引擎處理深度集成,使其在極端條件下更加強大。

在我們看來,這項專利目前可能不太引人注目,但其影響深遠。蘋果不僅僅是在改進相機軟件,而是從芯片層面重新定義圖像傳感器。如果這項技術投入生產,我們可能會看到數字成像領域的全新黃金標準——不僅在智能手機領域,也在電影領域。

四、具有高動態範圍和低噪聲的堆疊像素圖像傳感器

目前使用的絕大多數圖像傳感器都是CMOS(互補金屬氧化物半導體)有源像素傳感器(APS)單片陣列,具有4T像素。在這些器件中,每個探測器元件(稱為「像素」)包含一個光電二極管、一個浮動擴散區和四個CMOS晶體管,其中包括一個傳輸門、一個復位門、一個選擇門和一個源極跟隨器讀出晶體管。傳輸門控制從光電二極管到浮動擴散區的電荷轉移,並通過相關雙採樣(CDS)實現降噪。使用3T像素(沒有傳輸門)的圖像傳感器更容易製造,也更不容易出現僞影,但通常噪聲較高。

概括:

下文描述的本發明實施例提供了改進的圖像傳感器以及用於生產和控制此類圖像傳感器的方法。

因此,根據本發明的一個實施例,提供了一種圖像傳感器,該圖像傳感器包括一個邏輯芯片,該邏輯芯片包含列讀出電路和連接到列讀出電路的位線,以及一個覆蓋在邏輯芯片上的傳感器芯片。該圖像傳感器包括一個探測器元件陣列,每個探測器元件包括一個設定在傳感器芯片上的傳感電路和一個設定在邏輯芯片上的像素電路。

該傳感電路包括一個具有陰極和陽極端子的光電二極管、一個連接到光電二極管其中一個端子的浮動擴散節點、一個耦合在浮動擴散節點和復位電壓之間的復位晶體管,以及一個具有連接到浮動擴散節點的輸入和輸出的源極跟隨器晶體管。

像素電路包括一個選擇晶體管,該選擇晶體管具有耦合到源極跟隨器的輸出的輸入和耦合到其中一條位線的輸出,以及一個電流存儲器電路,該電流存儲器電路耦合到選擇晶體管的輸入,並配置為感測和輸出指示檢測器元件中的噪聲水平的信號。

在一些實施例中,每個感測電路包括一個橫向溢流積分電容(LOFIC)電路,該電路包括一個或多個電荷存儲電容以及耦合在浮動擴散節點和電荷存儲電容之間的一個或多個LOFIC晶體管,其中,復位晶體管耦合在LOFIC電路和復位電壓之間。

在一個公開的實施例中,該LOFIC電路包括:具有第一電容的第一電荷存儲電容;具有大於第一電容的第二電容的第二電荷存儲電容;連接在浮動擴散節點和第一電荷存儲電容的第一電荷輸入端之間的第一LOFIC晶體管;以及連接在第一電荷存儲電容的第一電荷輸入端和第二電荷存儲電容的第二電荷輸入端之間的第二LOFIC晶體管。

在一個實施例中,復位晶體管連接在第二電荷存儲電容的第二電荷輸入端和復位電壓之間。此外或可選地,在將檢測器元件讀出到位線期間,第一和第二LOFIC晶體管依次導通,同時選擇晶體管導通。

在一些實施例中,在每個圖像幀期間,復位晶體管在第一復位周期內導通,以在幀的曝光周期之前復位浮動擴散節點;選擇晶體管在曝光周期之後的第一讀出周期內導通,以從浮動擴散節點讀出光電荷。然後,復位晶體管在第一選擇周期之後的第二復位周期內導通,以復位浮動擴散節點;選擇晶體管在第二復位周期之後的第二讀出周期內導通,以讀出探測器元件累積的噪聲。

在一些實施例中,電流存儲電路包括至少一個採樣電容器和至少一個採樣晶體管,它們耦合在選擇晶體管的輸入端和至少一個採樣電容器之間,其中,至少一個採樣晶體管在第一和第二復位周期內跟隨復位晶體管導通,使得至少一個採樣電容器對探測器元件中的kTC噪聲進行採樣。

在公開的實施例中,電流存儲電路包括:連接在選擇晶體管的輸入端和至少一個採樣晶體管之間的讀取晶體管;以及與讀取晶體管並聯的、極性與讀取晶體管相反的偏置晶體管。其中,讀取晶體管和偏置晶體管在第一和第二讀出周期導通,在曝光周期截止。在一個實施例中,偏置晶體管在第一和第二復位周期導通。

另外或可替代地,至少一個採樣電容器包括第一和第二採樣電容器,並且至少一個採樣晶體管包括第一和第二採樣晶體管,它們串聯耦合在第一和第二採樣電容器與選擇晶體管的輸入端之間。

根據本發明的一個實施例,還提供了一種圖像感測方法,該方法包括:提供一個邏輯芯片,該邏輯芯片包括列讀出電路和連接到列讀出電路的位線;以及在邏輯芯片上覆蓋一個傳感器芯片。在傳感器芯片和邏輯芯片上形成一個探測器元件陣列,每個探測器元件包括一個形成在傳感器芯片上的感測電路和一個形成在邏輯芯片上的像素電路。

每個感測電路包括一個具有陰極和陽極端子的光電二極管、一個連接到光電二極管其中一個端子的浮動擴散節點、一個耦合在浮動擴散節點和復位電壓之間的復位晶體管,以及一個具有連接到浮動擴散節點的輸入和輸出的源極跟隨器晶體管。

每個像素電路包括一個選擇晶體管,該選擇晶體管具有耦合到源極跟隨器的輸出的輸入和耦合到其中一條位線的輸出,以及一個電流存儲器電路,該電流存儲器電路耦合到選擇晶體管的輸入並配置為感測和輸出指示檢測器元件中的噪聲水平的信號。

通過以下結合附圖對本發明實施例的詳細描述,將更全面地理解本發明:

實施例詳細說明

本文描述的本發明實施例提供了一種包含新穎設計的3T像素的圖像傳感器,該傳感器可實現高動態範圍、低噪聲,並且不會出現傳統4T像素陣列中可能出現的僞影。該圖像傳感器包含一個堆疊在邏輯芯片上的傳感器芯片。

每個3T像素在傳感器芯片上包含一個傳感電路,該電路包括一個光電二極管和一個橫向溢流積分電容(LOFIC)電路,以便在從室內到明亮陽光的各種光照條件下進行傳感,而無需自動曝光控制。此外,每個像素在邏輯芯片上包含一個像素電路,該像素電路包含一個電流存儲電路。該電流存儲電路用於感測探測器元件中的噪聲水平。電流存儲電路輸出的信號能夠利用CDS抑制熱噪聲(kTC)。

雖然邏輯芯片上的電流存儲電路與LOFIC電路配合使用特別有用,但在其他實施例中,即使沒有LOFIC電路,邏輯芯片上的組件也可用於降低其他圖像傳感器像素中的噪聲。

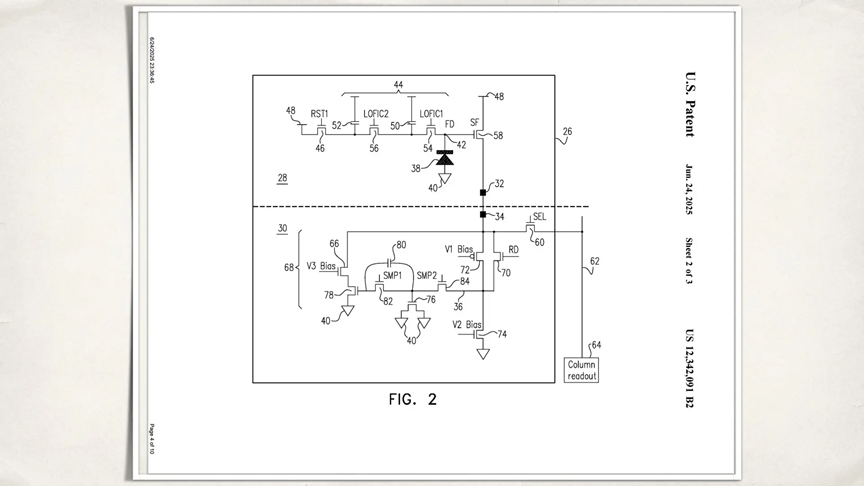

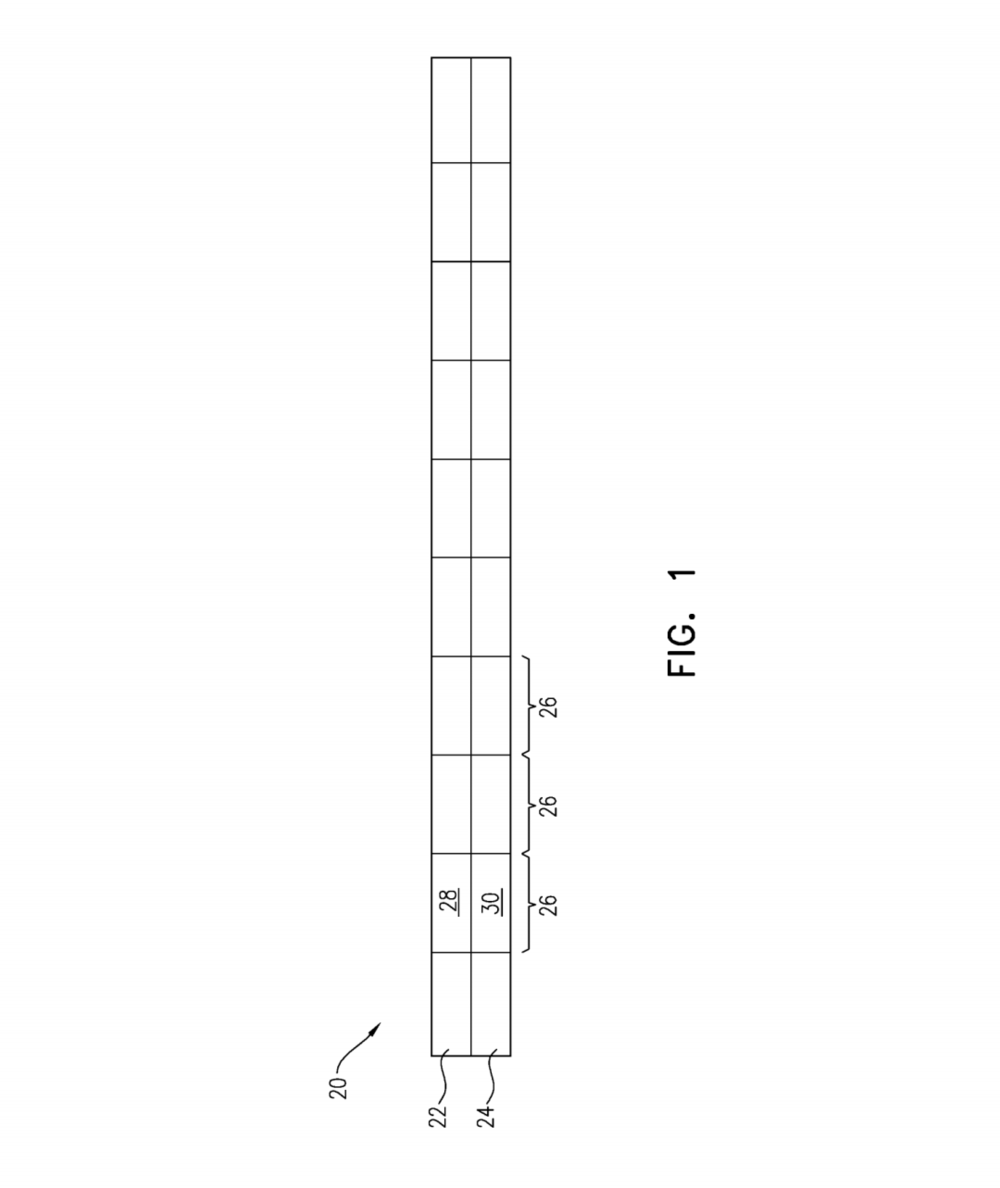

圖1是根據本發明實施例的圖像傳感器的示意側視圖;

圖1是根據本發明實施例的圖像傳感器20的示意側視圖。圖像傳感器20包括由一個硅芯片製成的邏輯芯片24,以及由另一個硅片製成的傳感器芯片22,該芯片覆蓋在邏輯芯片24上。圖像傳感器20包含一個探測器元件陣列26(也稱為像素),每個探測器元件包括位於傳感器芯片22上的傳感電路28和位於邏輯芯片24上的像素電路30。像素電路30通過位線連接到列讀出電路(如圖2所示)。圖像傳感器20的堆疊硅片配置使得在邏輯芯片24中使用標準CMOS控制和讀出電路成為可能,而傳感電路28可以通過不同的工藝製造。或者,傳感器芯片22可以包含除硅之外的其他半導體材料。

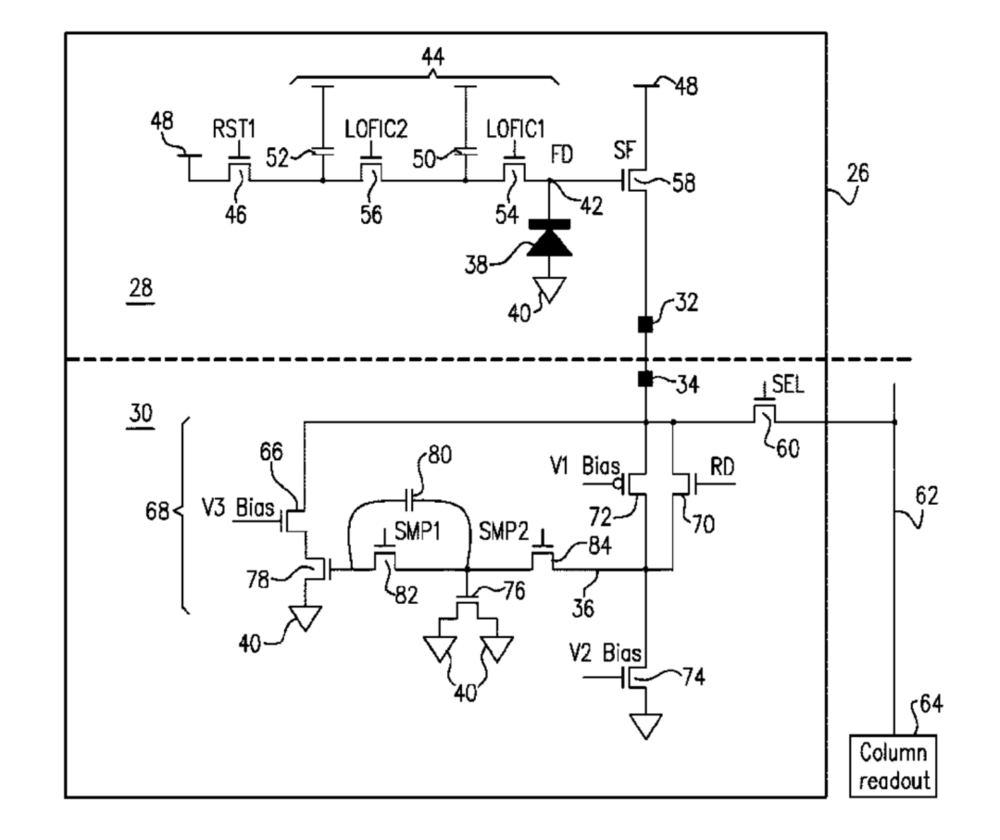

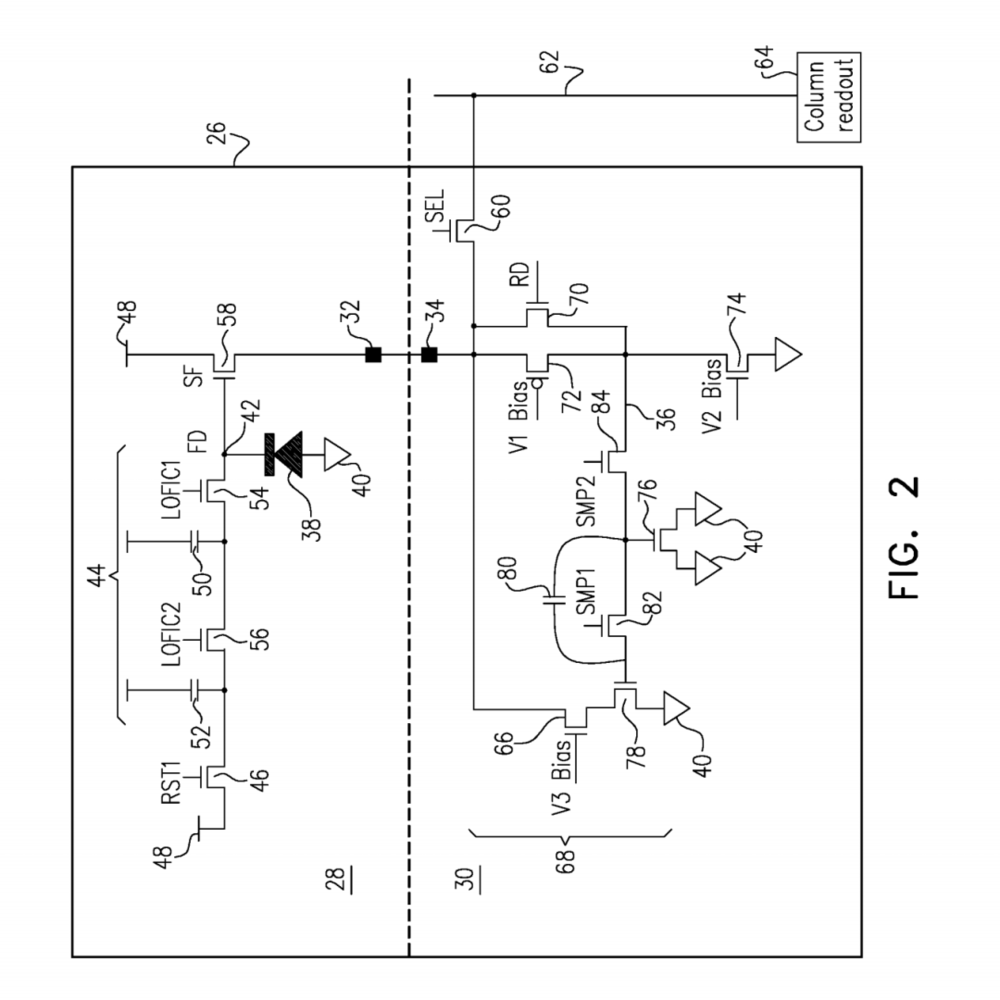

圖2是根據本發明實施例的圖像傳感器中探測器元件細節的示意電路圖;

圖2是根據本發明實施例的探測器元件26之一的示意電路圖。圖2中所示的傳感電路28包含N溝道MOSFET晶體管和N-on-P光電二極管38。或者,傳感電路28也可以包含P溝道晶體管和P-on-N光電二極管。傳感電路28的組件連接到電源電壓48,例如1.5 V、1.2 V或1.0 V。在本設計中,無需將電壓升壓至高於電源電壓或低於地電位。

傳感電路28包含一個浮動擴散節點(FD:floating diffusion)42,該節點連接到光電二極管38的一個端子(在本例中連接到陰極,陽極連接到地40)。橫向溢流積分電容(LO-FIC)電路44耦合至浮動擴散節點42,復位晶體管(RST1)46耦合於LOFIC電路和復位電壓(在圖示示例中,該復位電壓為電源電壓48)之間。

本示例中的LOFIC電路44包括兩個電荷存儲電容器50和52,以及兩個串聯耦合至浮動擴散節點42的LOFIC晶體管(LOFIC1和LOFIC2)54和56。第一個LOFIC晶體管(LOFIC1)54將浮動擴散節點連接到第一個電荷存儲電容器50的電荷輸入端,該電容器具有較小的電容,例如約為20 fF。

第二個LOFIC晶體管56將第一個電荷存儲電容器50的電荷輸入端連接到第二個電荷存儲電容器52的電荷輸入端,該電容器具有較大的電容,例如約為500 fF。在該配置中,浮動擴散節點42本身將用於在弱光條件下存儲和讀出光電荷;電荷存儲電容器50將用於在中等光照條件下存儲和讀出光電荷;電荷存儲電容器52將用於在強光條件下存儲和讀出光電荷。該LOFIC配置使探測器元件26能夠感測約120 dB動態範圍內的光。或者,也可以使用其他LOFIC配置,其中電容器和晶體管的數量可以更少或更多。

源極跟隨器晶體管(SF:source follower transistor)58的柵極連接用於接收來自浮動擴散節點42的電荷輸入,其漏極連接到輸出端子32,該輸出端子與像素電路30的輸入端子34連接。輸入端子34連接到選擇晶體管(SEL)60。當選擇晶體管導通時,它會將來自探測器元件26的信號輸出到位線62,該位線為探測器元件陣列的提供服務。

如上所述,該位線將傳感器芯片22中的探測器元件連接到邏輯芯片24中的列讀出電路64。在從探測器元件26讀出數據期間,連接到輸入端子34的偏置晶體管(V3 Bias)66處於關閉狀態,通常消耗約1 uA的電流。

為了實現噪聲感測和消除,像素電路30包含一個電流存儲電路68,該電路包含一個N溝道讀取晶體管(RD:read transistor)70和一個P溝道偏置晶體管(V1 Bias)72並聯。本例中的讀取晶體管和偏置晶體管極性相反。因此,在圖示的示例中,讀取晶體管70(以及像素電路30的其他組件)是N溝道器件,而V1 Bias晶體管72是P溝道器件。第二個偏置晶體管(V2 Bias)74與P溝道偏置晶體管串聯,當兩個偏置晶體管導通時,會吸收偏置電流,例如約100 nA。

採樣線36連接到讀取晶體管70和V1偏置晶體管72的漏極以及V2偏置晶體管74的源極。從檢測器元件26流出的電流由一對採樣電容器76、78採樣,這對採樣電容器連接在採樣線36和地40之間。這些採樣電容器76、78可以具有低電容,例如每個約為4 fF,並且兩個採樣電容器之間存在大約0.1 fF的附加寄生耦合80。

為了在感測電路復位期間對流經感測電路28的電流進行採樣,一對採樣晶體管(SMP1和SMP2)82、84會短暫地同時導通。然後,晶體管82(SMP1)關閉,接着晶體管84(SMP2)也關閉。晶體管82對探測器元件26的kTC噪聲進行採樣,而晶體管84對晶體管82關閉後的殘餘誤差進行採樣。因此,kTC噪聲被採樣,並通過流入和流出採樣電容器78的電流進行補償。

在從探測器元件26讀出期間,採樣的電流信號由選擇晶體管60讀出到位線62。或者,電流存儲電路68可以僅包含一個採樣電容器,也可以包含更多數量的採樣電容器,並相應地佈置一個或多個採樣晶體管。

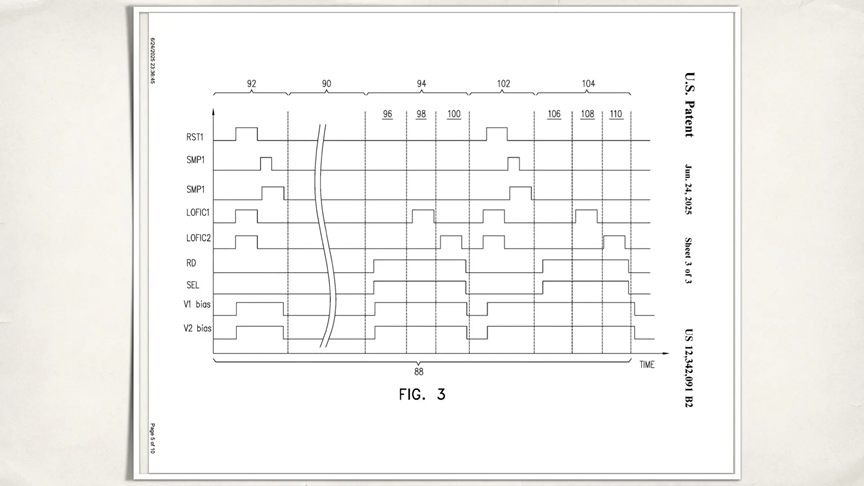

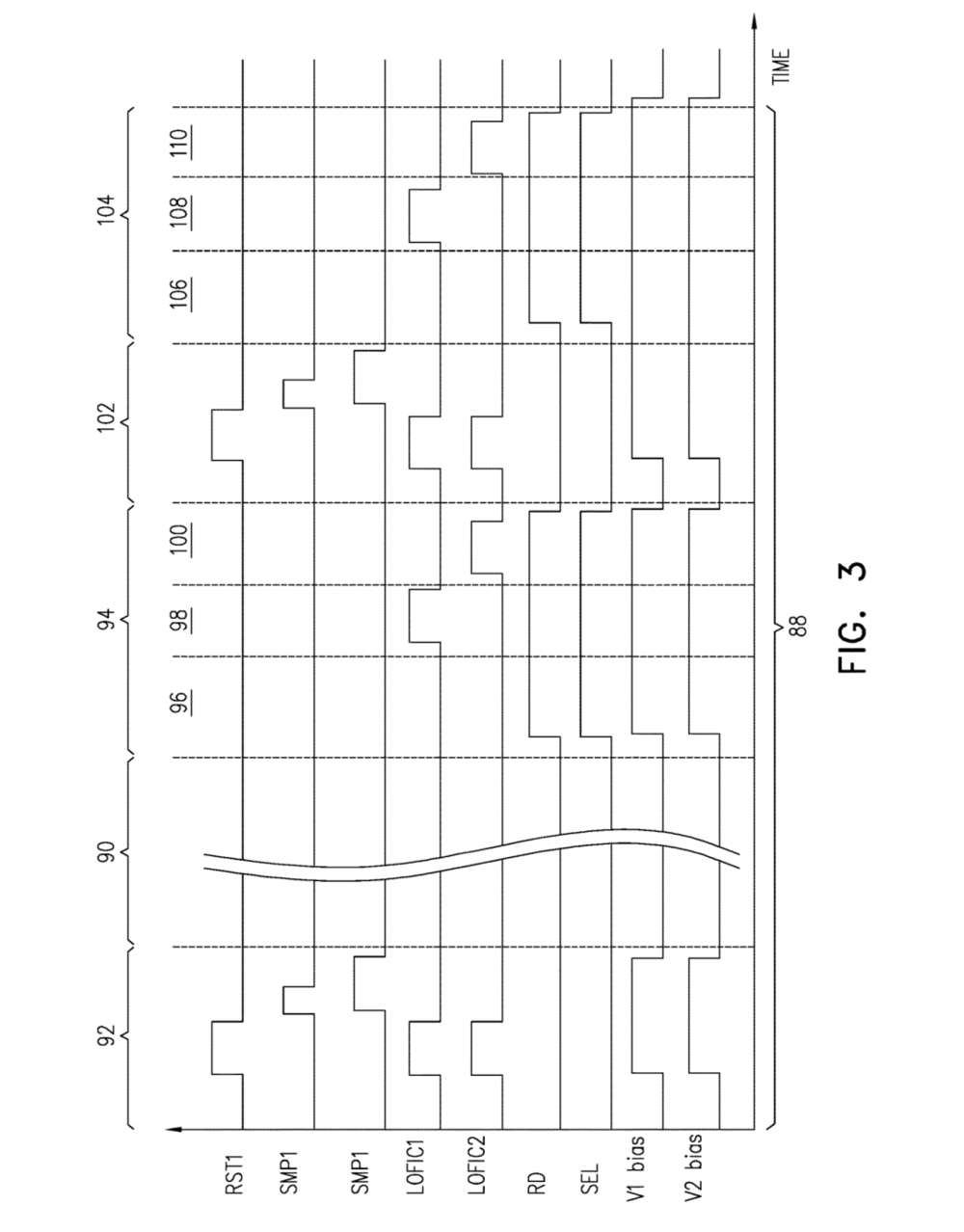

圖3是根據本發明實施例的時序圖,示意性地示出了施加到圖2中探測器元件晶體管的信號

圖3為時序圖,示意性地示出了根據本發明實施例的在單個圖像幀88過程中施加到探測器元件26的晶體管46、54、56、66、70、72、74、82和84的信號。為了簡化說明,施加到晶體管72的V1偏置信號顯示為與其他信號具有相同的極性;但實際上,由於V1偏置晶體管72是P溝道器件,因此V1偏置信號的極性將與其他信號的極性相反。施加到晶體管66的V3偏置信號與V2偏置信號相同,因此為了簡單起見,此處省略。

每個圖像幀88包括曝光期90,例如在1-10毫秒的範圍內,在此期間,來自光電二極管的光電荷在浮動擴散節點42處收集,並且可能在LOFIC電荷存儲電容器50、52中的一個或兩個上收集,具體取決於入射光的強度。在曝光期90之前的預曝光復位期92中,復位晶體管(RST1)46導通,以復位浮動擴散節點42。LOFIC晶體管54、56也與RST1一起導通,以復位LOFIC電荷存儲電容器50、52。

此外,在曝光期之前的復位期內,像素電路30中的偏置晶體管72、74、66(V1 Bias、V2 Bias和V3 Bias)均導通,採樣晶體管82、84(SMP1和SMP2)在RST1復位脈衝之後導通,然後依次關閉。

在曝光周期90之後,選擇晶體管60和讀取晶體管70(SEL和RD)在讀出周期94期間導通,同時三個偏置晶體管72、74和66(V1 Bias、V2 Bias和V3 Bias)也導通,以將光電荷從浮動擴散節點42讀出到位線62。讀出周期94包括高增益間隔96、中增益間隔98和低增益間隔100。當選擇晶體管60導通時,浮動擴散節點42上的電荷首先在高增益間隔96期間被讀出。然後,LOFIC晶體管54和56依次在中增益間隔98和低增益間隔100期間導通,以將存儲在LOFIC電荷存儲電容器50和52中的光電荷讀出到位線62。

所有光電荷讀出後,復位晶體管在曝光後復位周期102中,(RST1)46與兩個LOFIC晶體管54、56再次導通,以復位浮動擴散節點42和LOFIC電荷存儲電容器54、56。像素電路30中的偏置晶體管72、74、66(V1 Bias、V2 Bias和V3 Bias)再次全部導通,採樣晶體管82、84(SMP1和SMP2)在RST1復位脈衝後導通,然後依次關斷,就像在復位周期92期間一樣。

在這些復位之後,選擇晶體管60和讀取晶體管70在噪聲讀出周期104期間再次導通,以讀出探測器元件26積累的噪聲。噪聲讀出周期104包括高增益間隔106、隨後的中增益間隔108和低增益間隔110。當選擇晶體管60和讀取晶體管70導通時,浮動擴散節點42上的電荷首先在高增益間隔106期間被讀出。然後,LOFIC晶體管54和56依次在中增益間隔108和低增益間隔110期間導通,以將LOFIC電荷存儲電容器52和54中剩餘的電荷讀出到位線62。

在噪聲讀出周期104期間,偏置晶體管72、74和66保持導通。電流存儲電路68感測並輸出指示探測器元件26中噪聲水平的信號。邏輯芯片24中的CDS電路(未示出)從曝光周期後讀出的光信號中減去在此第二讀出周期讀出的噪聲信號,從而降低圖像傳感器20輸出信號中的噪聲影響。

應當理解,上述實施例僅作為示例引用,本發明不限於上述具體顯示和描述的內容。相反,本發明的範圍包括上述各種特徵的組合和子組合,以及本領域技術人員在閱讀前述說明後能夠想到的、且在現有技術中未公開的變體和修改。