炒股就看金麒麟分析師研報,權威,專業,及時,全面,助您挖掘潛力主題機會!

(來源:愛集微)

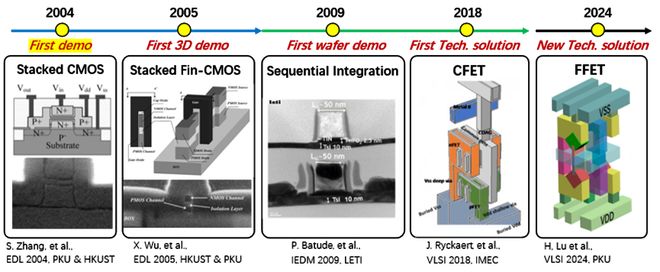

三維晶體管結構包括FinFET和GAA FET等,是半導體工藝演進中的關鍵性突破之一,其重要性在於解決了傳統平面晶體管在納米尺度下的物理極限問題,支撐了摩爾定律的延續。2011年,英特爾成功量產採用FinFET的處理器;2022年,三星電子成為全球首家在3納米工藝中量產採用GAA結構的邏輯半導體的公司;2025年,台積電將量產2納米工藝,採用GAA結構。這些都有效推進了半導體技術工藝的演進發展。而在第42屆超大規模集成電路研討會(VLSI 2025)上,北京大學微電子學院黃如院士團隊公布了新一代三維晶體管結構「倒裝堆疊晶體管(Flip FET, FFET)」,首次實現了8層晶體管的三維垂直集成,單位面積邏輯密度較傳統FinFET提升3.2倍,功耗降低58%。這一突破性成果被業界視為延續摩爾定律的最具潛力方案之一。

三維晶體管技術持續演進

受人工智能、高性能計算、數據中心等應用的推動,近年來半導體先進邏輯工藝的市場規模不斷擴大,直接推動了全球半導體產業的成長。市調機構Counterpoint Research最新報告顯示,全球純半導體晶圓代工行業收入預計在2025年將按年增長17%,超過1650億美元。先進的3nm和5/4nm節點在推動半導體收入增長方面發揮着關鍵作用,預計2025年3nm節點的收入將按年增長超過600%,達到約300億美元;包括 7nm在內的先進節點將在2025年貢獻純晶圓廠總收入的一半以上。

然而在技術層面,傳統的二維平面集成方式面臨物理極限和工藝極限的瓶頸,當晶體管尺寸縮小至20nm以下時,柵極對溝道的控制力減弱,導致漏電流劇增、功耗失控,三維堆疊成為接續摩爾定律演進的主要方向。

從目前業界的發展進程來看,FinFET解決平面晶體管失效問題,在10年內支撐了從16nm到5nm的跨越。3nm/2nm以下GAA 將接棒,確保芯片在功耗、性能、集成度上的持續進步。三星電子2022年首家量產採用GAA結構的3納米工藝;2025年台積電將採用GAA量產2nm工藝,同時計劃在2027年後推出N2P、N2X等2nm的變體工藝,進一步優化性能與功耗。

至於再下一代的三維晶體管結構,IMEC於2018年提出的補場效應晶體管(Complementary FET, CFET)被認為是一個有力的競爭者。根據此前IMEC公布的技術路線圖,憑藉CFET,芯片工藝技術在2032年將有望進化到5埃米(0.5nm),2036年有望實現2埃米(0.2nm)。台積電、三星、英特爾等都在實驗室中對CFET進行了預研開發。

北大 Flip FET 實現架構創新

不過隨着近年來在半導體技術研發投入上的增加,我國在新一代三維晶體管結構上也開始發出自己的聲音。北京大學吳恒研究員-黃如院士團隊在2024年6月召開的集成電路頂級會議VLSI2024上,首次提出了FlipFET技術。在今年召開的VLSI2025上,北大團隊再次發布相關研究成果。根據北京大學集成電路學院發布的消息,在VLSI2025上北京大學集成電路學院共有12篇高水平學術論文入選。其中「倒裝堆疊晶體管的高密度集成驗證」和「面向亞1nm節點的倒裝堆疊晶體管演進路線圖」,都受到極大關注。

根據相關報道,在3D堆疊晶體管和背面互連技術等新型架構的開發過程中,面臨着高深寬比工藝難點以及設計複雜性等挑戰。FlipFET通過自對準地背靠背堆疊正面(FS)NFET和背面(BS)PFET,並結合雙面電源/信號互連,可實現高密度的晶體管和互連線集成。在此基礎上,為獲得完整晶圓級集成結果,經過一年多的打磨,北京大學吳恒研究員-黃如教授團隊開發了一系列關鍵工藝模塊,包括晶圓鍵合、襯底減薄、背面溝道形貌優化以及背面光刻對準校正,成功獲得了FlipFET的關鍵正反面器件電性,並報道了世界首個背部集成的邏輯晶體管技術。

實驗結果表明,正面NFET經過翻轉表現良好,背面PFET性能優異(最小溝長低至30 nm,SS=73.1 mV/dec,DIBL=24 mV,開關比達107),與正面NFET相當。FlipFET還展現出天然分離柵結構、約500 mV的多閾值電壓可調性以及實現雙面CMOS的能力,顯著優於傳統的單片CFET。這些進展驗證了FlipFET在工藝可實現性、設計靈活性和可擴展性方面的巨大潛力,使其成為超越1nm邏輯節點的重要候選技術。

在面向亞1nm節點的倒裝堆疊晶體管演進路線圖的研究中,北大團隊針對A2及以下工藝節點面臨的功耗、性能與面積(PPA)挑戰,提出了三代結構創新:1)完全自對準倒裝堆疊晶體管F3ET,實現正反面柵極的自對準,提高設計靈活性並降低柵極互連電阻;2)基於叉形晶體管的完全自對準倒裝堆疊晶體管F4ET,並結合嵌入式供電軌(embedded Power Rail)及背面接觸(Backside Contact),實現了極致2T標準單元設計;3)基於互補堆疊晶體管的倒裝堆疊晶體管CFFET,實現四層晶體管的終極堆疊。

同時,研究還拓展至SRAM的微縮路徑,基於多種倒裝堆疊SRAM架構方案,成功實現了FFET SRAM在A2節點下的同步縮放。該研究構建出一套面向極限尺度的DTCO優化路徑,驗證了FFET面向亞1nm先進邏輯晶體管微縮的潛力。

CFET與中國Flip FET的技術探索

就半導體工藝技術而言,所有的現代計算機芯片都是由晶體管組成的。經典的平面晶體管結構都包含一個柵極、一個源極和一個漏極,並排列在一個二維平面上。當人們對柵極施加一個電壓,柵極就會打開,電流從源極流向漏極,電路就會導通。這是現代計算機芯片最基礎的結構。但隨着晶體管的尺寸不斷縮小,特別是溝道的尺寸也隨之縮小,人們面臨的問題也隨之增加,人們的解決方案是改變晶體管的結構。從二維平面變為三維立體,從FinFET、GAA到CFET以及Flip FET,目標都是提高晶體管密度,改善高漏電等問題。

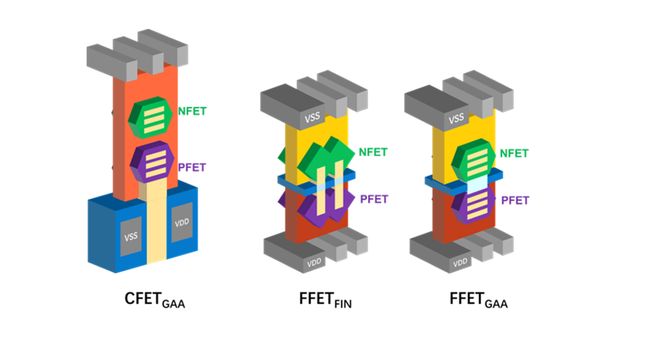

CFET的目的就是在單一集成工藝中將n型(nFET)和p型(pFET)晶體管堆疊在一起,通過晶體管級的三維堆疊集成,在晶體管結構上作出改變,以便更高效地利用空間,提升器件密度和性能。

據芯思想報道,晶體管級的三維集成技術目前已經受到廣泛關注。其設計思路是通過在垂直方向上堆疊器件和互連,將傳統的單面佈局擴展至多面空間,在掩模版尺寸受限的條件下為單芯片提供了突破集成密度上限的可能。

相較而言,CFET的核心是將n型和p型晶體管縱向堆疊於同一單元內,直接壓縮水平面積。Flip FET則是在晶圓正面製作nFET,背面製作pFET,通過晶圓翻轉實現雙面器件堆疊。結合背面電源軌(BPR)與雙面信號互連,單元高度可降至5T以下,且供電電阻降低40%,電壓穩定性更優。CFET以直接n-p堆疊實現面積減半,但FFET通過雙面分離設計提升供電效率和設計靈活性,在超高密度場景(如1納米以下)更具擴展性。

吳恒研究員也特別指出,Flip FET並不是一種器件結構技術,而是器件三維集成的新架構。其不僅適用於Fin結構的堆疊,還適用於下一代GAA納米片,具有很強的拓展性。

更加值得關注的是,FFET還充分結合了中國大陸當前的設備情況,可以兼容現有產線,採用非EUV依賴工藝。據業內人士透露,其可在7nm工藝上進行,利用成熟設備,有效降低了產業化的門檻。這種集成思路可以依賴現有光刻技術和設計能力將集成電路的集成度持續提升,更適應中國本土產業鏈現狀。

中國方案的機遇與考驗

可以說,Flip FET 的發布,打破了中國在先進邏輯器件領域長期「跟跑」的被動局面,在全球半導體科研領域發出了自己的聲音。這也引發台積電、英特爾等巨頭的高度關注。台積電研發總監指出,該技術「重新定義了三維集成的技術邊界」。

有中國台灣地區業者表示,Flip FET充分利用晶圓背部進行晶體管級三維堆疊,融合了晶圓背部互連和堆疊晶體管集成方法,能提升芯片集成密度和電路設計靈活度。通過創新方案實現類似CFET的PPA,展現了中國大陸業者的研發韌性。

當然,FlipFET面臨的挑戰還有很多,例如,FlipFET晶圓需要進行減薄工藝和多個背面工藝流程,更容易受到晶圓翹曲和套刻誤差的影響,從而降低良率,增加成本。此外,晶圓翻轉後,細間距觸點和金屬的對準也是一個問題。目前的Flip FET還處於研發階段,未來實現量產仍需面臨諸多挑戰。

在摩爾定律放緩的背景下,半導體行業面臨技術瓶頸。如何持續優化芯片的性能(Performance)、功耗(Power)和麪積(Area),已成為全球產業界與學術界共同攻堅的核心命題。Flip FET通過引入雙面有源區與雙面互連等創新設計,將晶圓集成從傳統的單面加工推向三維立體化,為突破摩爾定律桎梏提供了全新範式。相信未來會有更多中國方案被提出。