炒股就看金麒麟分析師研報,權威,專業,及時,全面,助您挖掘潛力主題機會!

(來源:超能網)

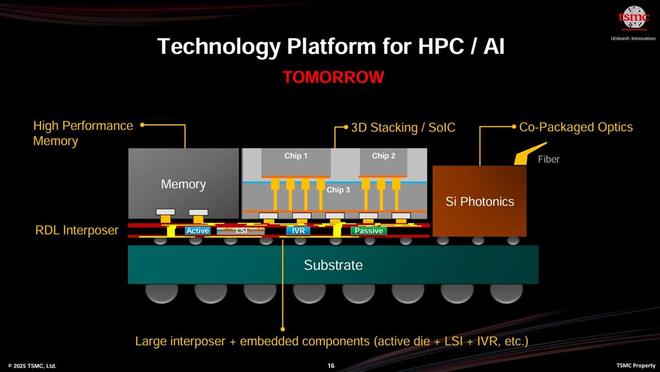

近年來,台積電(TSMC)除了積極投資先進製程節點,以保證競爭優勢外,還逐步加大了在封裝技術方面的投入力度,以滿足新一代人工智能(AI)和高性能計算(HPC)芯片的需求。其中準備了新一代CoPoS(Chip-on-Panel-on-Substrate)封裝技術,可以將基板擴展到310 × 310 mm甚至更大尺寸。

據DigiTimes報道,台積電正在準備改變先進封裝戰略,將CoWoS「面板化」,與扇出型面板級封裝(FOPLP)技術整合,過渡到CoPoS封裝技術。未來將採用方形基板,取代過去的圓型基板,這麼做可以有效提升產能。

台積電計劃最早於2026年建立首條oPoS封裝生產線,進行試點生產,負責的工廠是中國台灣嘉義AP7的P4和P5,最快2028年末至2029年上半年量產,預計未來CoPoS將取代CoWoS-L。台積電已經大致敲定了首批設備的供應廠商,確立相關規格與訂單量。

與FOPLP一樣,CoPoS也採用大型面板基板進行封裝,不過兩者存在一些差異。FOPLP是一種不需要中介層的封裝方法,芯片直接重新分佈在面板基板上,並通過重分佈層(RDL)互連。這種方法具有成本低、I/O密度高、外形尺寸靈活等優勢,適用於邊緣AI、移動設備和集成密度適中的中端ASIC等應用。CoPoS則引入了中介層,從而有着更高的信號完整性和穩定的功率傳輸,對於集成GPU和HBM芯片的高端產品來說效果更好。同時中介層材料正從傳統的硅變為玻璃,將提供更高的成本效益和熱穩定性。