如台積電所說,直接硅基液冷(Direct-to-silicon liquid cooling)技術在應對高性能計算/人工智能應用中由2.5D/3D先進封裝帶來的高功率和高功率密度方面展現出巨大潛力。

在本文中,台積電的工程師在3.3倍光刻CoWoS-R封裝上演示了一種基於硅的液冷解決方案——硅集成微型冷卻器(IMC-Si)。該集成方案僅需對現有的CoWoS工藝流程進行少量修改。在硅邏輯芯片和液冷歧管蓋之間塗覆了一種抗翹曲密封劑,形成用於直接液冷的防漏氣室。該集成系統使用40℃水作為冷卻劑,在10 LPM的流速下,能夠均勻散熱高達3.4 kW(在1.6倍光刻SoC上為2.5 W/mm²)的功率。

採用源自典型數據中心環境的臨界水泄漏率 115 cc/year (氦氣泄漏率為 4.4 x 10⁻⁶ Pa·m³/s)來評估密封劑的穩健性和可靠性。實驗結果表明,該集成系統通過了包括多次迴流焊(3 個循環)、熱循環測試(2000 個循環)和高溫超導測試(150 °C,1000 小時)在內的壓力測試,氦氣泄漏率至少比臨界泄漏率低一個數量級。

此外,還進行了加速液體浸沒測試(150 °C,4.8 bar 壓力),以評估密封劑的抗液體泄漏性能。首次成功證明,與 IMC-Si 集成的 CoWoS 是一種可行的解決方案,能夠滿足日益苛刻的高性能計算/人工智能應用中對熱性能和電性能的要求。

引言

最先進的人工智能 (AI) 模型飛速發展,導致模型規模的增長速度遠遠超過了摩爾定律。為了跟上步伐,異構集成各種芯片已成為超越傳統邏輯擴展性能提升的必要手段。通過將邏輯和存儲器集成在中介層上,可以顯著縮小它們之間的距離,從而通過提高能效和帶寬來增強計算性能。芯片的 3D 堆疊(例如 TSMC 的 SoIC)由於垂直方向上芯片間距的顯著減小,能夠提供更大的性能提升。

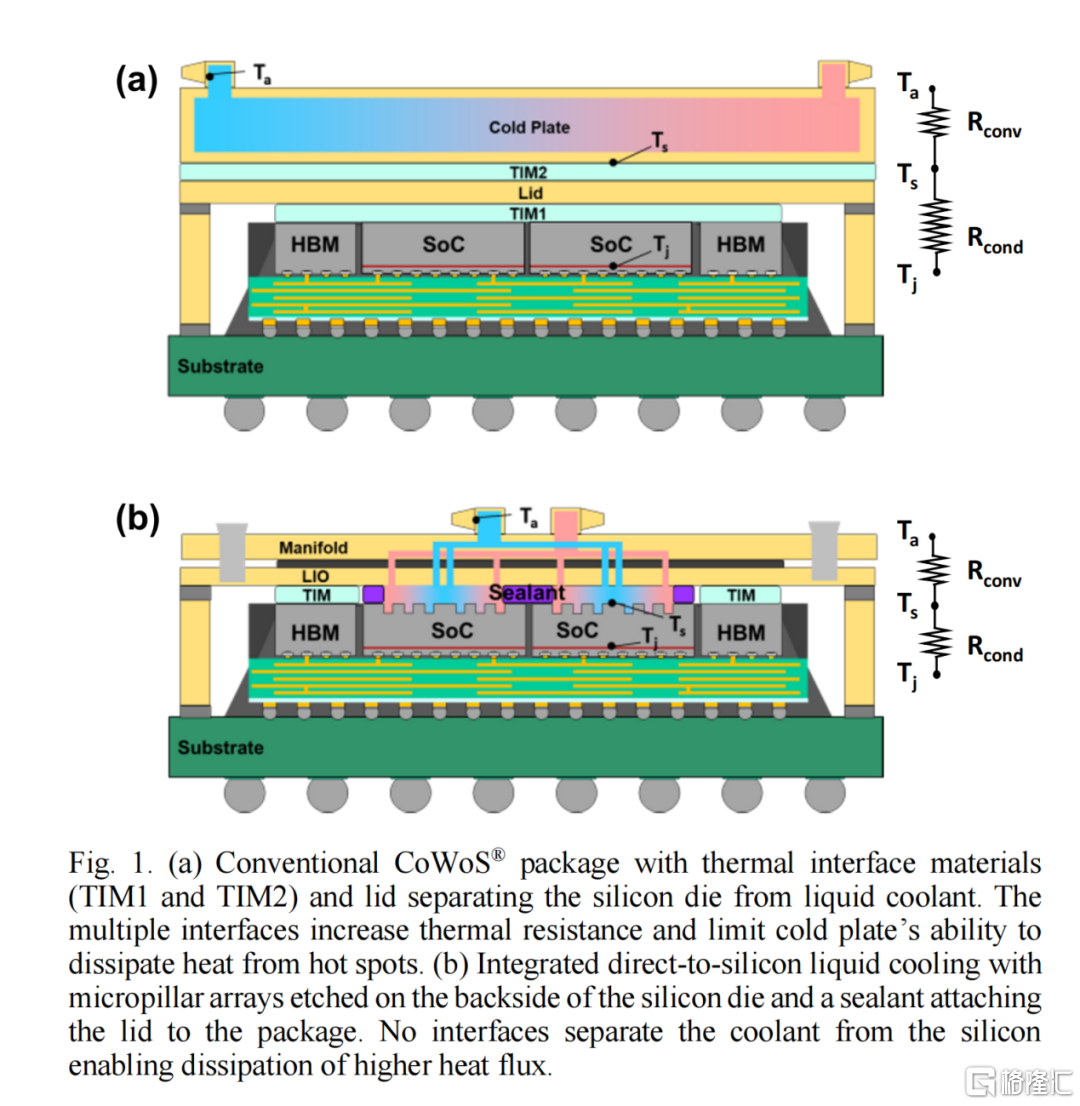

然而,集成系統在高功率密度下散熱的能力限制了異構集成未來性能的提升。最簡單的情況是,垂直堆疊兩個邏輯芯片會使功率密度翻倍。近年來,液冷板因其優於風冷的散熱效率而被集成到高性能計算 (HPC) 應用中。然而,如圖 1(a) 所示,它們的間接液體冷卻方案(包括沿傳熱路徑的熱界面材料 (TIM))限制了其在高功率密度應用中的冷卻效率。

直接硅液冷技術通過將液態冷卻劑直接輸送到硅芯片背面來解決這一問題,如圖 1(b) 所示。多項研究證實,直接硅液冷技術比傳統冷板具有更高的功率密度。我們之前關於硅集成微型冷卻器 (IMC-Si) 的研究表明,該冷卻器採用直接液冷技術,在集成於 0.8 倍光罩熱測試芯片 (TTV) 硅背面的交錯微柱陣列上進行冷卻,在均勻熱通量下,其冷卻能力可高達 2 kW,相當於 3.2 W/mm² 的功率密度。此外,在 1 kW 背景加熱的情況下,該冷卻器還能將局部熱點冷卻至 18 W/mm²。

儘管直接硅液冷技術比傳統冷板具有更高的冷卻能力,但其在數據中心的部署需要與現有異構集成系統兼容,並在各種環境條件下具備強大的防漏可靠性。大多數高性能計算 (HPC) 應用採用台積電的晶圓基芯片封裝 (CoWoS) 平台,以實現大尺寸中介層,從而為多個芯片組提供高密度互連和高帶寬的芯片間通信。

直接硅液冷解決方案必須證明其與 CoWoS 平台兼容,才能在未來的數據中心部署中得到應用。以往的直接硅液冷演示並未強調其與先進封裝的兼容性,並且採用了不適用於大規模生產的液體密封機制。這些演示通常使用墊片或 O 形圈進行固體密封,但由於翹曲和拓撲結構變化的增加,這些密封方式難以擴展到更大的封裝尺寸。

我們之前在 IMC-Si 方面的工作為與 CoWoS 平台的集成指明瞭方向,即使用可分散的聚合物基粘合劑作為邏輯芯片和歧管蓋之間的密封劑。這種彈性體密封劑可以有效緩解大尺寸封裝中的翹曲變化,並有助於多芯片密封。

本研究首次成功地將直接硅基液冷解決方案 IMC-Si 集成到 3.3X CoWoS-R 封裝上。該集成系統使用 40 °C 水作為冷卻劑,在 10 LPM 的流速下,可為邏輯芯片(1.6X 光罩)提供 3.4 kW 的冷卻功率,並實現 2.5 W/mm² 的均勻熱通量。將 IMC-Si 集成到 CoWoS®平台上僅需對現有的 CoWoS工藝流程進行少量修改。此外,該集成封裝在各種加速應力條件下(包括多次迴流焊、溫度循環 (TCG) 和高溫存儲 (HTS))均表現出良好的抗液漏性能。我們還驗證了密封劑在高溫高壓條件下長時間浸液後仍能有效防止液漏。這項工作為未來在高性能計算 (HPC) 數據中心部署集成 IMC-Si 和 CoWoS 平台的封裝奠定了基礎。

集成 3.3 倍 CoWoS-R 平台

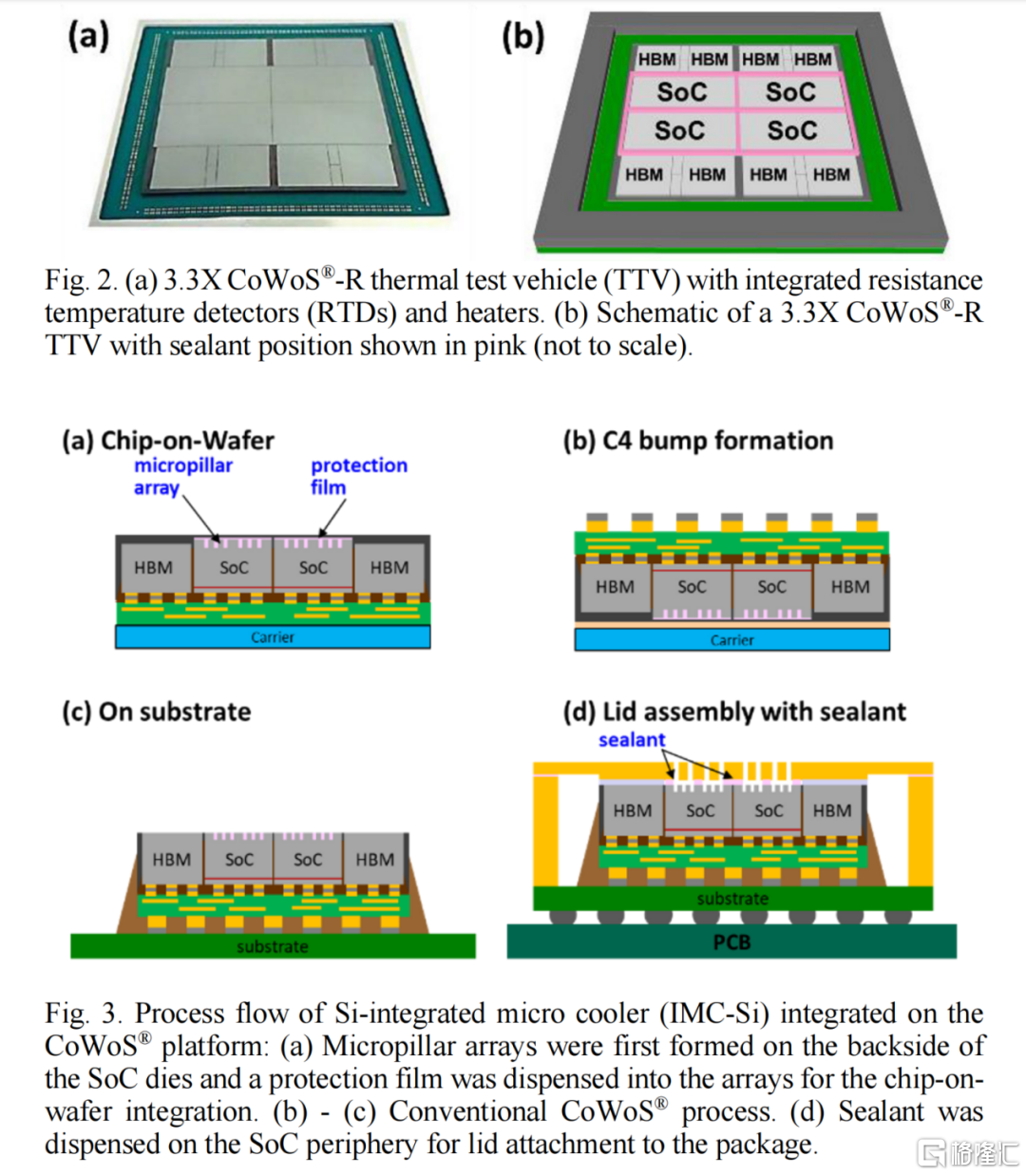

我們所提出的直接硅液冷解決方案 IMC Si 集成於 CoWoS-R 平台上。CoWoS-R 架構的主要優勢之一是能夠在保持高集成度的同時縮小封裝尺寸。有機中介層起到應力緩衝作用,通過緩解熱失配並改善熱循環條件下的焊點和互連完整性,從而提高機械可靠性。如圖 2(a) 所示,採用 3.3 倍 CoWoS-R TTV 封裝模擬中心包含 4 個邏輯系統芯片 (SoC) 芯片、外圍包含 8 個高帶寬存儲器 (HBM) 芯片的結構。

如圖 3 所示,將 IMC-Si 集成到 3.3X CoWoS-R 封裝上僅需對現有的 CoWoS-R 工藝流程進行極小的改動。該工藝流程首先在 SoC 背面形成微柱陣列,然後在陣列中塗覆一層保護膜。該保護膜符合傳統 CoWoS-R 工藝流程中的熱預算,且移除後不留任何殘留物。之後,如圖 2(b) 所示,在每個 SoC 的外周塗覆一層彈性密封劑。然後,將帶有多個與每個 SoC 腔室對齊的進出氣口的蓋子連接到封裝上。與傳統的覆蓋整個封裝表面的導熱界面材料 (TIM) 不同,該密封劑以一維線的形式塗覆在每個 SoC 芯片的周邊。這種結構使得密封劑能夠更好地適應大尺寸封裝的翹曲,同時保持蓋子和 SoC 之間良好的物理接觸。迴流焊後,將一個具有單個進出口的歧管組裝到集成系統上,該歧管旨在實現多個冷卻隔室之間的均勻流量分配。

熱測試結果

A. 實驗裝置

3.3X CoWoS-R 封裝包含兩種尺寸的 TTV:13.0 x 25.9 mm² 的芯片用於模擬 SoC 芯片,11.0 x 11.0 mm² 的芯片用於模擬 HBM 芯片。採用開爾文型電阻溫度檢測器 (RTD) 監測溫度變化。RTD 在溫度控制良好的烘箱中進行校準。RTD 溫度係數的平均值和標準偏差分別為 3.8 x 10⁻³ 和 9.0 x 10⁻⁶。每個 SoC 芯片上有五個 RTD;四個位於芯片的四個角,一個位於芯片的中心。由於密封劑的覆蓋和液體流動停滯,預計每個 SoC 芯片的四個角區域的結溫 (Tj,max) 最高。

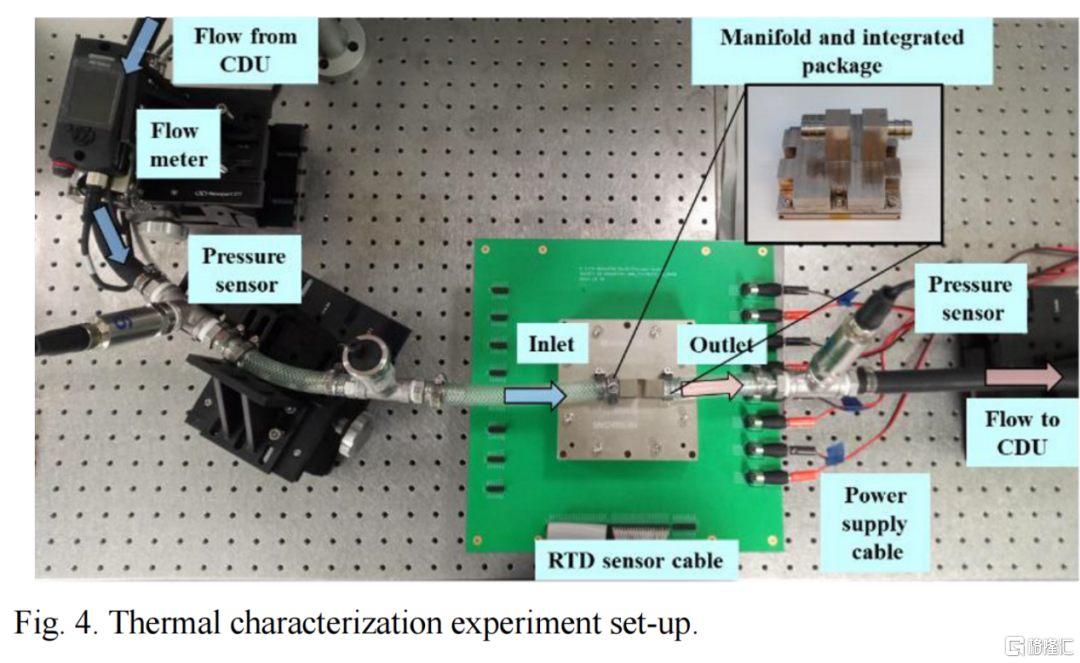

熱特性實驗是在閉環配置中,使用商用數據中心冷卻分配單元 (CDU) 進行的,如圖 4 所示。入口處使用 40 °C 的純水作為液體冷卻劑,入口冷卻劑與 Tj,max 之間的允許溫差 (ΔT) 設定為 60 °C。

B. 均勻加熱

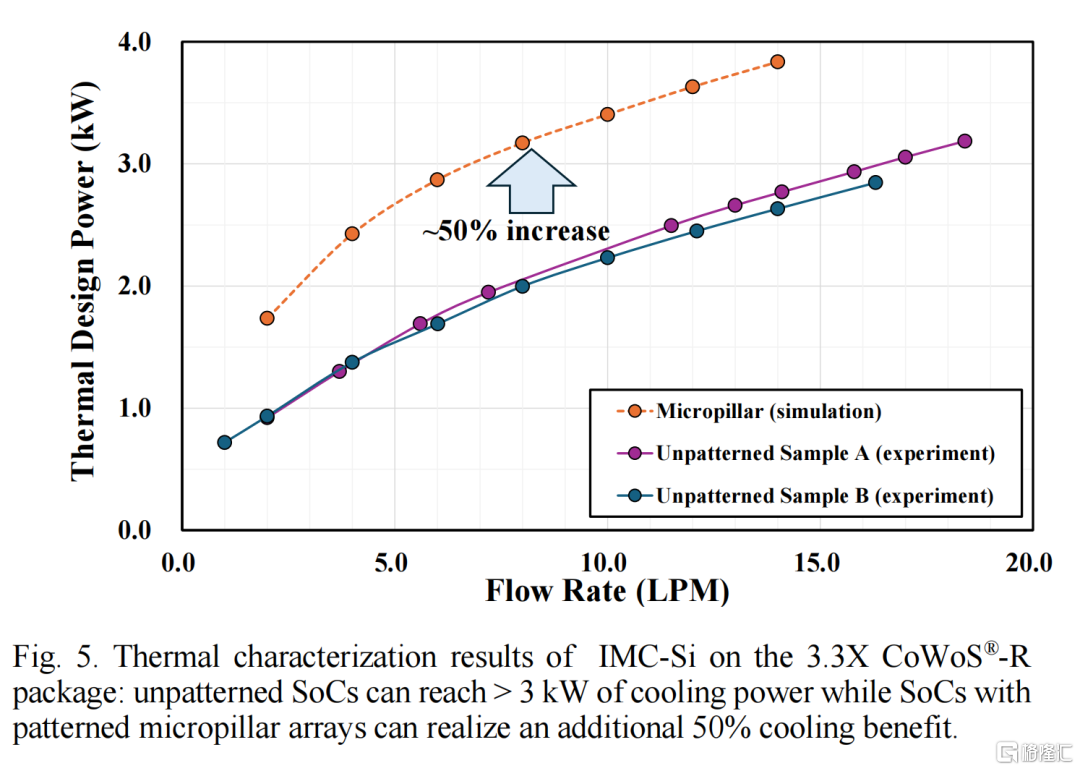

圖 5 展示了 3.3X CoWoS-R 封裝上 IMC Si 在不同流速下均勻熱流的熱特性測試結果。在總流速為 5.6 LPM(每個 SoC 約 1.4 LPM)的情況下,直接對 SoC 背面(未圖案化,且無微柱陣列)進行硅液冷,四個 SoC 的總冷卻能力可達 1.7 kW。由於無需 TIM 層及其相關的熱阻,冷卻液能夠更有效地散熱。此外,在達到「收益遞減」點之前,通過 IMC-Si 進行直接液冷可以提升較高的流速下的散熱性能,之後流速的進一步提升帶來的收益將非常有限。當總流速提升至 11.5 LPM 時,TDP 提升至 2.5 kW,功率密度達到 1.9 W/mm²。相比之下,間接冷卻系統(例如冷板)在流量顯著降低的情況下,其熱性能往往就會達到飽和。間接液體冷卻系統的總熱阻受限於多箇中間表面的傳導熱阻。

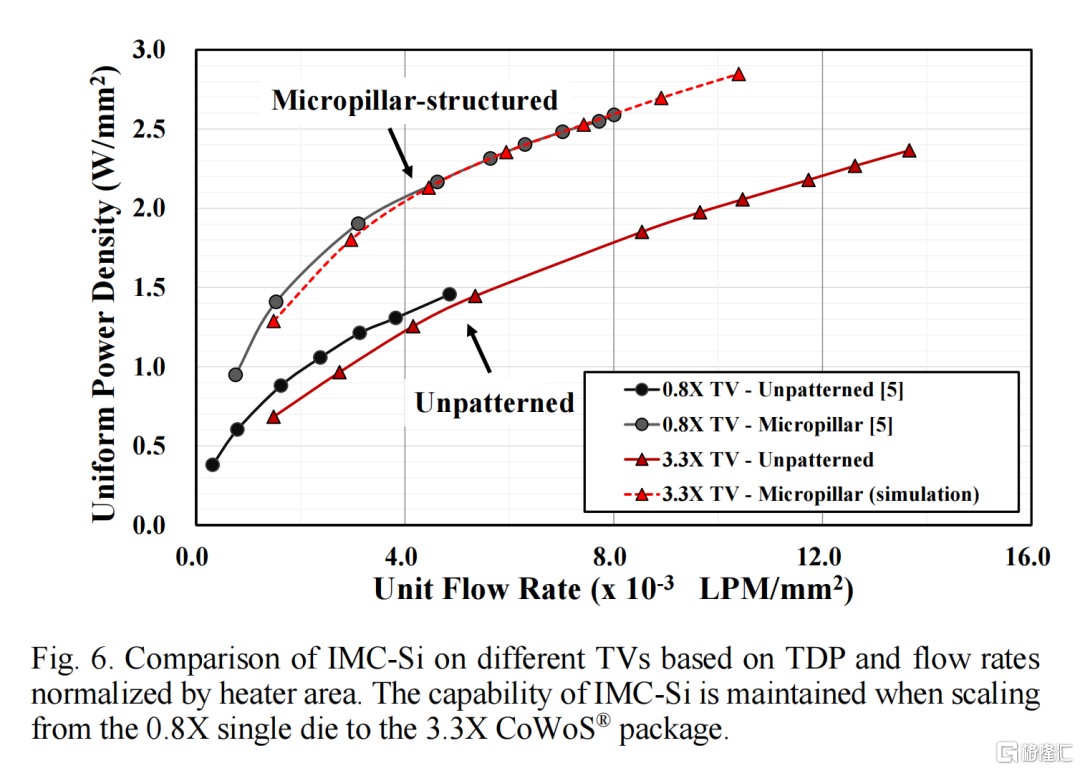

此外,仿真結果表明,如圖 5 所示,集成在 SoC 背面的微柱陣列可額外提升 50% 的散熱性能。這種提升歸因於表面積的增加和湍流的產生。在 10 LPM 的流速下,TDP 可提升至 3.4 kW,從而實現 2.5 W/mm² 的功率密度。我們之前對集成在 0.8X TTV 上的 IMC-Si 的熱特性分析結果也支持這一發現。圖 6 通過將 TDP 和流速除以加熱器面積或單位流速,比較了 0.8X TTV 和 3.3X CoWoS-R TTV 的熱性能。對於未圖案化表面上的 IMC-Si 液冷,0.8X TTV 和 3.3X TTV 的性能曲線相似。例如,在單位流速為 5 x 10⁻³ LPM/mm² 時,兩種 TTV 的功率密度約為 1.5 W/mm²。當在 SoC 背面形成微柱陣列時,3.3X TV 的仿真結果與 0.8X TV 的實驗數據幾乎完全重合。這表明,從 0.8X 單芯片擴展到 3.3X CoWoS 平台時,IMC-Si 的冷卻能力得以保持。

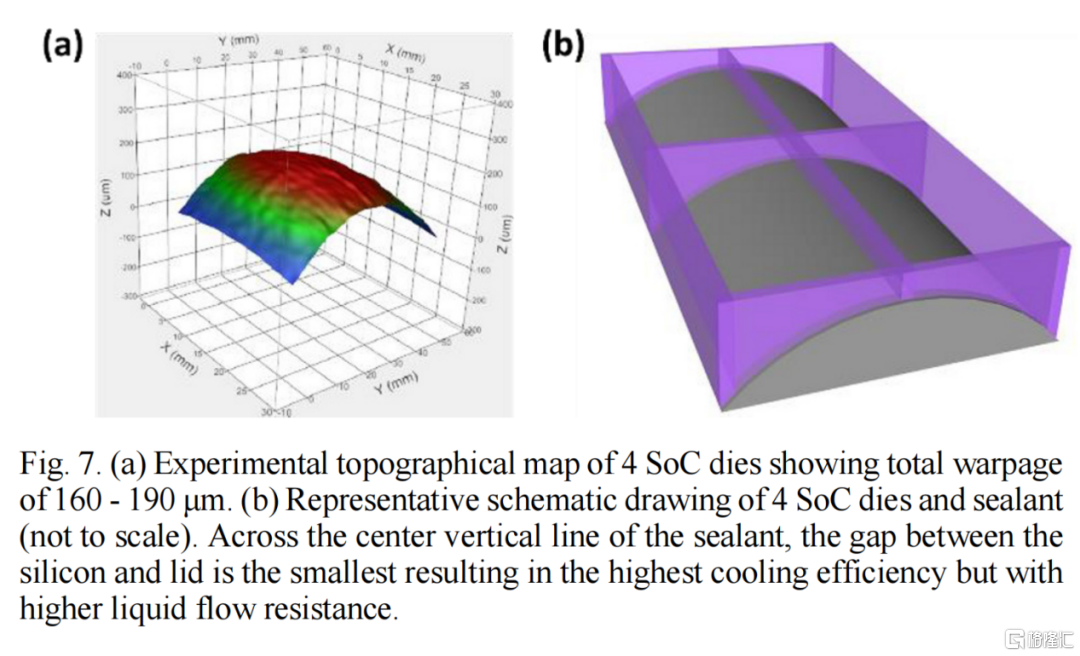

如圖 7(a) 所示,封裝尺寸較大以及多種材料集成導致的熱膨脹係數 (CTE) 不匹配,使得 3.3X CoWoS-R TTV 中的四個 SoC 芯片出現 160-190 µm 的翹曲。在傳統的帶冷板封裝中,這種翹曲通常會導致導熱界面材料 (TIM) 覆蓋不良或分層,從而降低其冷卻性能。然而,IMC-Si 中的彈性體密封劑可以緩解翹曲引起的冷卻問題。SoC 與蓋板之間的間隙大小對流體動力學和冷卻效率的影響截然不同。間隙越小,流動阻力越大;然而,由於更有效的傳熱路徑,冷卻效率反而會提高。如圖 7(b) 所示,在靠近中心垂直密封線的位置,間隙較小,流動阻力較高,但冷卻效率更高。相反,在邊緣處,間隙可增大 160-190 µm,導致流動阻力降低,但冷卻效率也隨之降低。

封裝可靠性表徵

A. 用於早期可靠性測試的氦氣泄漏測試

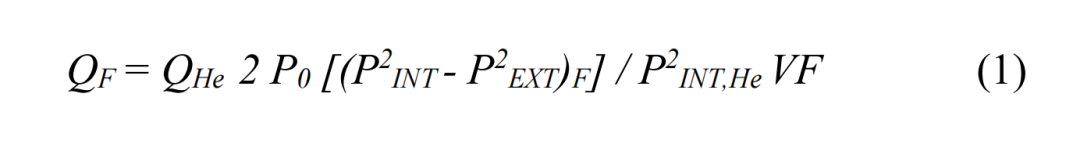

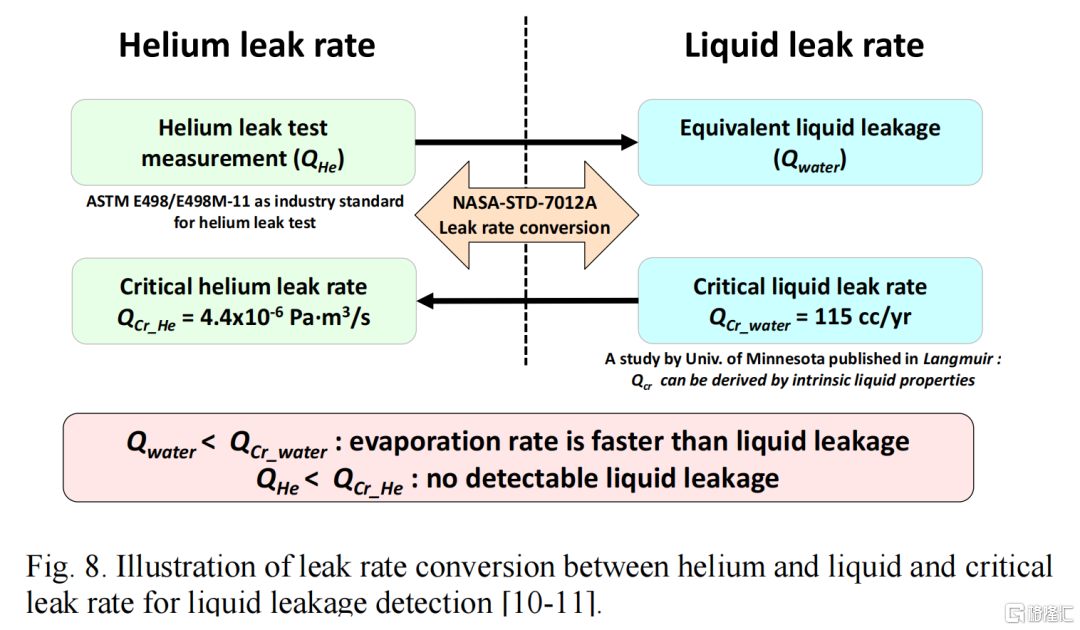

為了對 IMC-Si 集成 CoWoS-R 封裝進行早期可靠性測試,我們按照標準的 JEDEC 封裝可靠性測試方法評估了密封劑的防泄漏性能,並進行了額外的高壓高溫液體浸沒測試。鑑於 IMC-Si 液冷技術的創新性,目前尚無成熟的可靠性表徵方法。我們參考了數據中心行業組織開放計算項目 (OCP) 的液冷板可靠性測試指南,作為直接硅液冷的模板。根據 OCP 指南,由於氦氣分子尺寸小,可以識別極小的針孔泄漏,因此推薦使用氦氣進行泄漏檢測 ]。此外,我們參考了 NASA 標準 NASA-STD-7012A,對氦氣泄漏率和液體泄漏率進行了保守的換算:

其中,QF 為液體泄漏率,QHe 為氦氣泄漏率,PINT 和 PEXT 分別為液體 (F) 和氦氣 (He) 的內壓和外壓,VF 為氦氣與液體的動態粘度比,P0 為大氣壓。

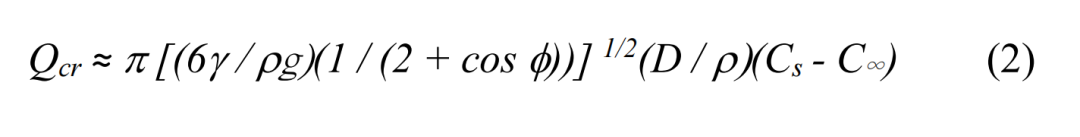

圖 8 概述了氦氣泄漏測試中泄漏率閾值(或臨界泄漏率)的推導過程。為了檢測液體泄漏,液體泄漏率必須超過典型數據中心環境下的蒸發速率。Extrand 等人解釋說,該臨界泄漏率可以根據液滴體積、接觸角和流體固有特性計算得出,如公式 (2) 所示:

其中 γ 為表面張力,ρ 為密度,g 為重力加速度,φ 為接觸角,D 為液體擴散係數,Cs 和 C∞ 分別為空氣和環境空氣中飽和蒸汽的濃度。利用該公式,數據中心的臨界泄漏率 (Qcr_water) 估計為 115 cc/year(水)。Qcr_water 可以轉換為臨界氦泄漏率 (Qcr_He),其值為 4.4 x 10⁻⁶ Pa·m³/s。換句話說,如果集成封裝的氦氣泄漏測試結果小於 Qcr_He,則表明不會發生可檢測到的液體泄漏。

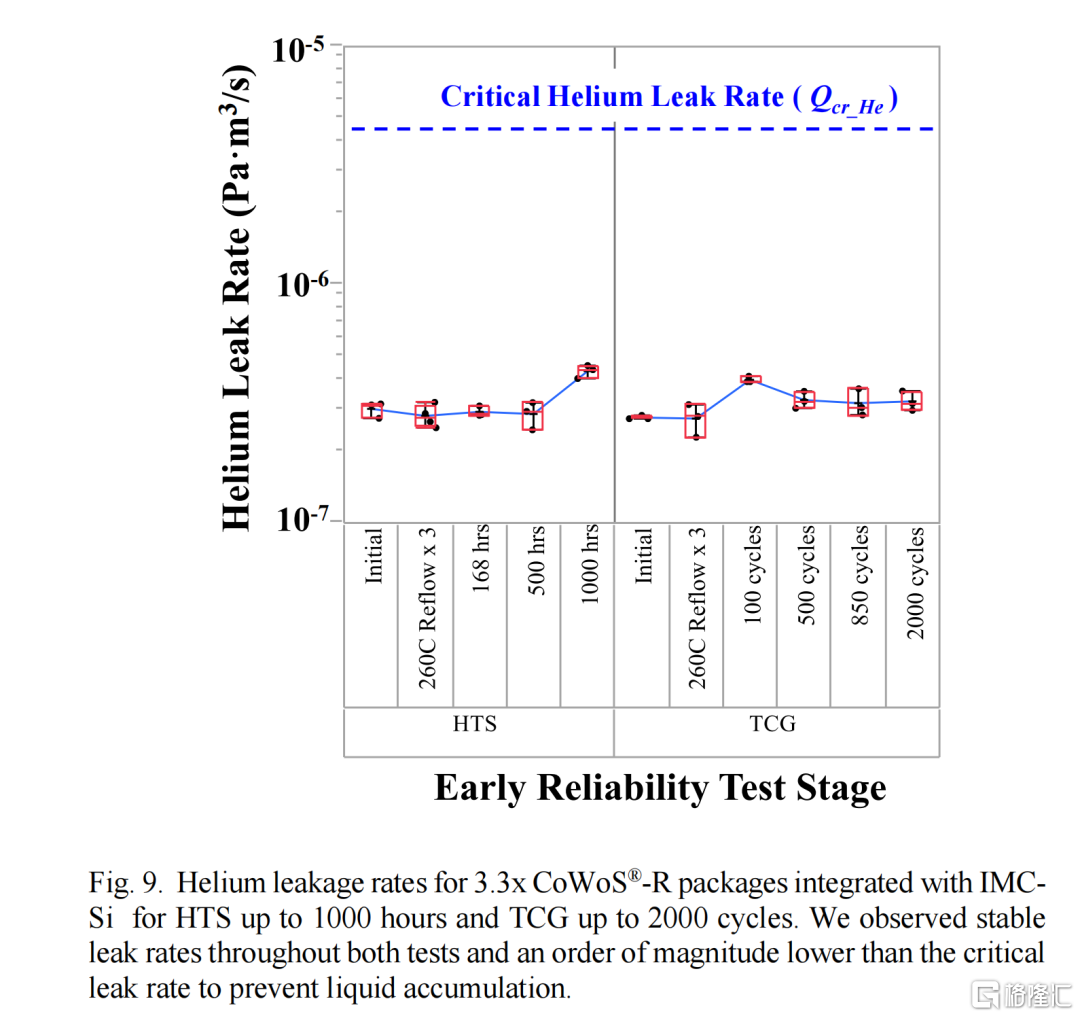

為了對IMC-Si集成3.3X CoWoS-R封裝進行氦氣泄漏測試,我們為封裝組裝了一個特製的單開口蓋和歧管。除密封區域外,所有可能的泄漏路徑均使用墊片和O型圈密封,以確保氦氣泄漏僅通過密封劑發生。我們向封裝內泵入1 bar的純氦氣作為示蹤氣體,以識別可能導致部署過程中水滲出的潛在泄漏點。氦氣泄漏檢測器檢測到了通過密封劑的任何氦氣泄漏。我們對樣品進行了標準JEDEC可靠性測試流程的典型階段測試,包括初始組裝、迴流焊後、TCG 100/500/850/2000次循環和HTS 200/500/1000小時,以監測密封劑的性能。

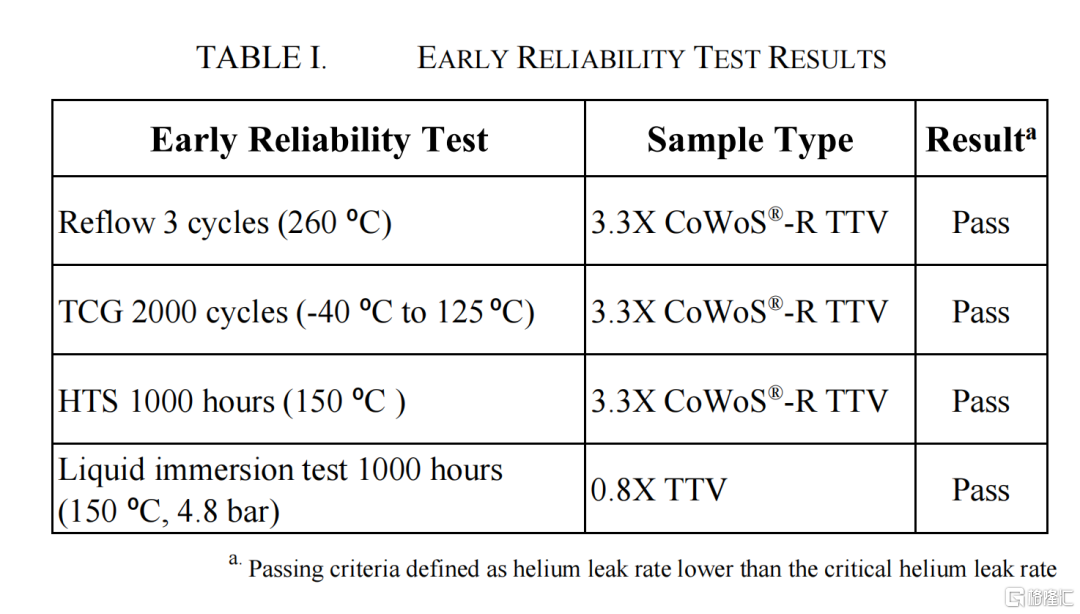

B. 早期可靠性測試結果

表 I 總結了 IMC-Si 集成 3.3X CoWoS-R 封裝的早期可靠性測試結果。該集成封裝成功通過了多次迴流焊、TCG 和 HTS 測試,氦氣泄漏率至少比 Qcr_He 低一個數量級。此外,如圖 9 所示,我們在整個 TCG 和 HTS 測試過程中觀察到穩定的氦氣泄漏率,這表明密封劑在高溫和長時間條件下具有良好的穩定性。TCG 測試中較大的溫度變化以及由此引起的封裝翹曲變化並未導致密封劑分層。通過 HTS 測試證實,在長時間的熱機械應力作用下,密封劑與蓋板和硅片之間仍保持着牢固的粘合力。

此外,我們還進行了一項加速測試,以評估密封劑在液體環境下的穩定性。將密封劑塗覆到單芯片測試載體上,並與金屬蓋板組裝在一起。隨後,將樣品浸入150℃、4.8巴壓力的去離子水中1000小時。這種嚴苛的環境旨在加速密封劑粘合性和完整性的任何化學降解。加速試驗後的氦氣泄漏測試結果遠低於Qcr_He值一個數量級。這表明該密封劑在液態冷卻劑中具有較長的使用壽命。

總結

我們首次在 CoWoS®平台上集成了一種直接硅基液冷解決方案 IMC-Si。通過在硅芯片上應用抗翹曲且無泄漏的密封劑,液冷液能夠流經硅芯片背面。集成的 3.3X CoWoS-R 封裝能夠散熱高達 3.4 kW 的功率,功率密度可達 2.5 W/mm²。氦氣泄漏測試和早期可靠性評估證實,該集成封裝的氦氣泄漏率始終低於臨界閾值一個數量級,並通過了應力測試和液體浸沒測試,且密封劑未發生劣化。

這些結果凸顯了集成在 CoWoS 平台上的 IMC-Si 在嚴苛環境下可靠應用的潛力和可擴展性,它能夠有效防止液體泄漏,並確保較長的使用壽命。未來的工作將着重於優化微柱設計並減少翹曲,以提高冷卻效率。

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅為了傳達一種不同的觀點,不代表半導體行業觀察對該觀讚好同或支持,如果有任何異議,歡迎聯繫半導體行業觀察。