硅光子技術正在改變數據中心,而最大的變革還在後面。

可插拔光模塊已在數據中心應用多年,並主導着橫向擴展連接。下圖是谷歌的 Jupiter 網絡,用於互連集羣中的數千個 Ironwood TPU。圖中大部分線纜為黃色,代表單模光纖 (SMF)。至於縱向擴展,英偉達 CEO 黃仁勳去年夏天曾表示,「我們應該儘可能長時間地使用銅纜。」 大多數觀察人士認為,最多還能再用兩到三代。

橫向擴展(scale-out )網絡中存在大量連接。每個機架都配備一個機架頂部 (TOR)以太網交換機,擁有 128 個以上的端口,其上方還有 1-2 層橫向擴展網絡。縱向擴展(scale-up )的鏈路數量則要多得多。例如,在 Nvidia NVL72 機架中,有 18 個交換機,每個交換機直接連接到 72 個 GPU 中的每一個:18 x 72 = 每個機架 1296 個鏈路。隨着 NVL144 和 NVL576 等更大規模的 pod,每個機架的縱向擴展鏈路數量也會增加。因此,當縱向擴展采用光纖時,光纖市場將會大幅增長。

在2025年光纖通信展(OFC 2025)上,OMDIA發布的光纖器件市場預測顯示,市場規模已從2003年的數十億美元(主要應用於電信領域)增長到2023年的約130億美元,此後增長速度將顯著加快,預計到2030年將達到250億美元,這主要得益於人工智能網絡的發展。首先是橫向擴展,幾年後是縱向擴展。CignalAI最新的預測則認為,到2029年,市場規模將達到310億美元。

圖 2:光器件市場總規模

光學元件包括:

硅光子學是將原本分散的光子器件集成到改進的CMOS工藝中;

激光器、硅光放大器(SOA)以及其他基於III-V族工藝(如磷化銦(InP)和砷化鎵(GaAs))製造的器件,以及封裝、光纖、連接器、適配器,用於在芯片之間提供連接。

本文重點介紹硅光子學。後續文章將討論其他關鍵組件。

光如何在芯片間傳輸數據

數據中心的銅纜正在向光纖過渡。實際的物理光連接由光纖電纜實現,這些電纜通常是「單模光纖」,用於傳輸單模或多波長的光。包層可以保護光纖,但更重要的是,包層的折射率低於纖芯,從而使光線集中在光纖中。光纖電纜市場規模龐大。市場領導者康寧公司每年銷售價值 68 億美元的光纖產品。Meta 公司最近與康寧公司達成了一項價值 60 億美元的協議,將在未來幾年內繼續供應光纖電纜。

圖 3:單模光纖電纜——實際光纖直徑為 8-9毫米,電纜直徑為 2-3 毫米

實際的光纖由玻璃製成,極其纖細——只有9毫米,也就是1/100毫米。如此細小的直徑使得光保持單模狀態,而硅光子學正是利用了這一點。

光纖通信中使用的波長是O波段、E波段、S波段、C波段和L波段,因為這些波段在光纖中的信號損耗相對較低。它們都位於紅外光譜範圍內。

圖 4:光纖中的光傳輸頻段

由於 O 波段在硅波導中的傳輸損耗低,因此被應用於硅光子學領域。

在光纖或芯片的波導中,可以使用單波長或多波長信號。多波長信號可以通過兩種方式實現:粗波分複用 (CWDM) 和密集波分複用 (DWDM)。CWDM 指的是波長之間的間隔相對較大;DWDM 指的是波長之間的間隔相對較小。CWDM 和 DWDM 都能提供更高的帶寬,但它們的實現挑戰各不相同。

請注意,儘管幾乎所有用於互連的光纖都是 SMF(單模光纖),但它們不一定可以互操作,因為光可以在單個或多個波長、不同波長和/或使用不同的連接器上傳輸。

硅光子學應用

可插拔光器件

硅光子學目前在數據中心市場的主要驅動力是可插拔光收發器。

它們是一種標準化的熱插拔設備,一端連接到交換機或服務器的電氣接口,另一端連接到光纖。與它們所取代的銅纜相比,它們能夠以更高的帶寬和更低的功耗,通過光纖將數據從一個交換機/服務器高速傳輸到另一個交換機/服務器。

可插拔光收發器的主要組件包括:1)激光器;2)具有DSP功能和高速SerDes的CMOS芯片;以及3)硅光子芯片。在這些收發器中,硅光子調製器(通常為馬赫-曾德爾調製器)對激光進行調製,以疊加來自CMOS芯片的數據。此外,還有濾波器、耦合器、石榴石、透鏡和隔離器。所有這些組件都封裝在標準化的可插拔封裝中。

Coherent 的 2025 年投資者報告預測,可插拔光器件市場將從 2023 年的 60 億美元增長到 2030 年的 250 億美元!到 2030 年,市場將主要以1.6T(1.6 太比特/秒)和 3.2T 數據速率為主,一些速度較慢的傳統產品仍將繼續出貨。

光路交換機 (OCS)

谷歌多年來一直在谷歌雲中使用光路交換機 (OCS) 。

與其他AI加速器不同,谷歌的TPU無需交換機,採用三維路由結構,可實現數千個TPU組成的集羣。其機架頂部(TOR)交換機使用可插拔光模塊,並連接到OCS層,從而實現整個數據中心頂層互連的重新配置。這對於冗餘、可靠性和應對不斷變化的工作負載的網絡重配置至關重要。谷歌的方案採用MEMS(微機電系統)鏡,這些微鏡可接收數百根輸入光纖,並將光路導向數百根輸出光纖中的任意一根。

圖 5:Google OCS 使用 MEMS 鏡像來路由/切換燈光

Lumentum 和 Coherent 目前也提供 OCS 技術,分別採用 MEMS(Lumentum)和液晶(Coherent)。在 2025 年 12 月的一次金融會議上,Coherent 的首席執行官表示:「我們非常看好 OCS。」去年夏天,他們預測 OCS 的潛在市場規模 (TAM) 將超過 20 億美元,但現在看到客戶興趣日益濃厚,應用領域也更加廣泛,因此他們將 TAM 的預估上調至超過 30 億美元。

多家初創公司正在利用更緊湊的硅光子技術開發「二維」光通信系統(OCS)。這些公司包括 iPronics、nEye 和 Salience。它們都在進行概念驗證樣品測試(nEye 和 Salience)或交付首批產品(iPronics)。這些技術最終可能比現有架構更經濟或更可靠。這些高密度解決方案也可能使 OCS 能夠應用於橫向擴展連接,首先用於冗餘/可靠性,然後用於全 GPU 到全 GPU 的 OCS 連接,甚至有一天可能取代硅分組交換機來實現橫向擴展。

共封裝光學器件 (CPO)

CPO可實現比可插拔光學器件更高的密度和更低的功耗。

隨着英偉達和博通宣佈將於 2025 年推出採用共封裝光器件的以太網橫向擴展交換機以降低交換功耗,CPO 已開始蠶食可插拔交換機的市場份額。

交換機是兩個芯片(上圖中紅色方框內),上方覆蓋着液冷外殼。從頂部伸出的四根粗黑電纜是液冷進出線。可插拔激光器(上圖中綠色方框內)位於圖片底部盒子的頂部,用於提供信號載波。共有9個激光器,每個盒子可能包含8個激光器。可以看到9根黃色電纜從激光器連接到交換機芯片。激光器採用可插拔設計是因為它們的故障率較高,這樣在發生故障時可以輕鬆更換,而無需更換整個交換機。左下角僅連接了一根輸入光纖——即黃色電纜。可以看到還有許多其他光纖連接器。從I/O面板到芯片的光纖連接必須位於我們看不到的下方。

CPO(可插拔式)的節能優勢(僅為可插拔式的三分之一)對於規模化應用而言意義重大,因為每個機架通常有超過1000個連接。Nvidia、Broadcom、Ayar Labs、Celestial(最近被Marvell收購)、Lightmatter和Ranovus都在致力於開發CPO解決方案。

如今,所有GPU/XPU/AI加速器都使用銅纜連接。正如英偉達的黃仁勳所指出的,目前的趨勢是儘可能長時間地使用銅纜。但銅纜的性能提升已接近收益遞減的瓶頸,更高的性能會導致連接距離過短,從而增加錯誤率。光纖連接將使AI加速器能夠以更低的延遲和更大的芯片容量,持續提升互連帶寬。

Ayar Labs 與 Alchip 於去年底展示了基於 CPO 的 AI 加速器概念圖。加速器和 HBM 芯片位於硅中介層上,而光引擎芯片(圖中展示了 8 個,包含超過 256 根光纖)則安裝在有機基板上。未來,光引擎將直接安裝在中介層上。

硅光代工,大有可為

與CMOS相比,目前的硅光子製造規模較小,但硅光子器件代工廠將迎來巨大增長,台積電或將成為第一。

目前主要的硅光子芯片代工廠商是GlobalFoundries(最近收購了AMF)和Tower Semiconductor。此外還有一些規模較小的廠商,例如提供原型製作服務的imec、荷蘭的LioniX以及馬來西亞的Silterra。台積電、三星和聯電都在為其代工產品開發硅光子芯片技術。

GlobalFoundries (GF)收購 AMF 後,聲稱已成為全球排名第一的硅光子(SiPho)代工廠,預計 2026 年 SiPho 收入將接近 3 億美元,到本十年末將超過 10 億美元。GF 硅光子副總裁兼總經理 Kevin Soukup 說,他們在新加坡擁有兩座晶圓廠,主要專注於 C 波段和 L 波段,主要用於長途相干應用。其中一座是他們收購的 AMF 晶圓廠,另一座是他們原有的規模更大的晶圓廠,該晶圓廠也採用 AMF 工藝。利用更大的晶圓廠,他們可以大幅提升產能,滿足長途客戶的需求。

在馬耳他,他們的 SiPho 晶圓廠專注於可插拔收發器和共封裝光學器件。他們擁有一種可以在芯片上製造 45nm CMOS 以及射頻和/或硅光子器件的工藝。他們還可以製造不含 CMOS 的 SiPho 芯片。他們利用其12nm FinFET工藝的先進設備來製造低損耗波導。他們還擁有類似於台積電COUPE工藝的技術,該工藝將電接口芯片(EIC)與光子集成芯片(PIC)集成到單個芯片中。他們支持光纖輸入的邊緣連接和頂部連接,但與COUPE不同的是,他們使用光學反射鏡進行頂部連接,將光反射90度角至邊緣連接,從而無需使用光柵耦合器。這使他們在寬帶領域具有優勢,因為光柵耦合器難以處理寬帶信號。Soukup表示,他們的客戶已在設計中「集成」了GF的CPO技術,以實現橫向擴展和縱向擴展。

GF還預測,2026年全球排名第二的硅磷晶圓代工廠營收約為2億美元,第三約為1億美元,第四約為5000萬美元。將這三家工廠的營收相加,並估算其餘工廠的營收,2026年硅磷晶圓代工廠的總營收將不足10億美元/年。這不到台積電年營收的1%。

Tower Semi 似乎是全球第二大硅光子器件代工廠。據介紹,Tower Semiconductor 的 PH18 SiPho 晶圓代工方案旨在滿足日益增長的 O 波段和 C 波段數據中心互連市場需求。該平台由 Tower Semiconductor 位於美國加利福尼亞州紐波特比奇的 200 毫米晶圓廠提供。我們、、公司便捷的多項目晶圓 (MPW) 穿梭測試計劃可提供低成本的快速原型製作服務。

與其他僅面向特定客戶或僅限於小批量原型製作的「封閉式」工藝不同,Tower Semiconductor 的「開放式」平台面向所有 SiPho 客戶開放。Tower Semiconductor 業界領先的設計平台,專為光網絡和數據中心互連應用而設計。SiPho 工藝與公司的 SiGe BiCMOS 工藝相輔相成,通過提供高速電子器件以及光器件,為不斷擴展的數據通信市場提供更完整的解決方案。

值得一提的是,在2024年,Tower推出了全新的300毫米硅光子(SiPho)工藝,並將其作為標準代工產品。據介紹,這項先進工藝是對Tower成熟的200毫米(PH18)平台(目前已實現量產)的有力補充,為客戶提供了一款尖端解決方案,旨在滿足下一代數據通信應用中日益增長的高速數據通信需求。

這款獨特的 300mm 晶圓採用業內一流的硅波導和最先進的低損耗氮化硅波導技術。更大的晶圓尺寸增強了與行業標準 OSAT(外包半導體封裝測試)平台的兼容性,從而有助於與電子元件無縫集成,並提高整體效率。

除了上述兩家公司以外,有些公司自行生產硅光子器件,例如英特爾和意法半導體。許多其他半導體/系統公司銷售的硅光子產品則由代工廠生產——例如,思科使用格羅方德(GlobalFoundries)的產品。

圖 8:硅光子晶圓收入預測

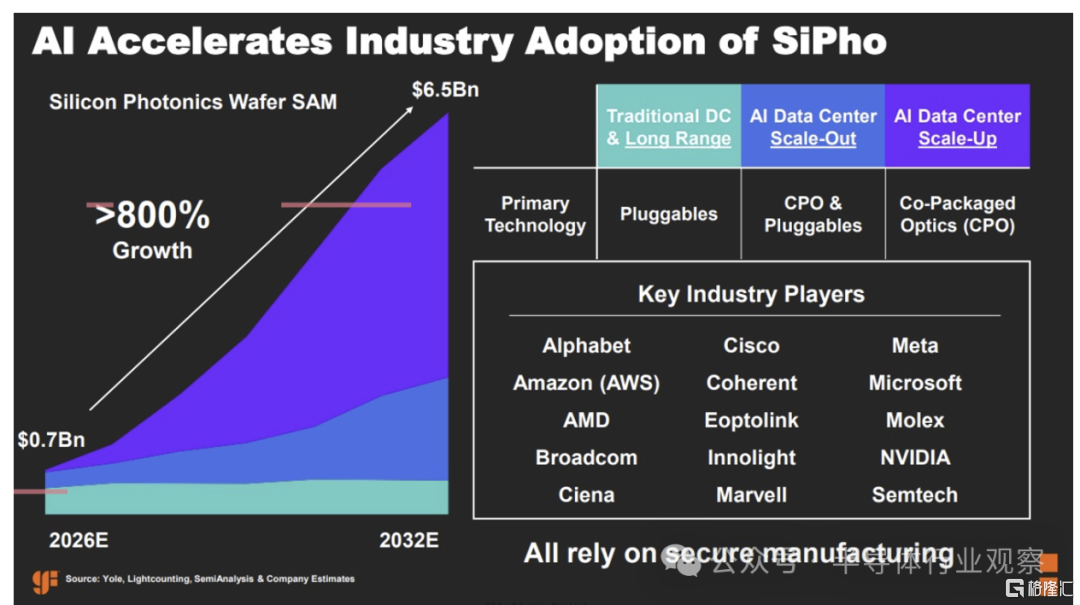

數據中心人工智能正推動硅光子代工廠實現迅猛增長:從2026年到2032年,短短六年間增長八倍。目前,橫向擴展是主要驅動力。幾年後,縱向擴展將成為最大驅動力,因為數據中心縱向擴展涉及的環節遠多於橫向擴展。

硅光子芯片的市場價值在出售時將遠高於芯片本身,因為封裝成本可能與芯片成本相當,且利潤率超過50%。DataM Intelligence預測,到2031年,硅光子集成電路市場規模將達到320億美元;Precedence Research預測,到2034年將達到290億美元。

橫向擴展(Scale-out)已開始向可插拔光器件(CPO)過渡,而縱向擴展(Scale-up)在不久的將來也需要CPO。縱向擴展需要CPO,是因為光子集成電路(PIC)必須足夠小,才能在GPU邊緣集成多個PIC,並且每個PIC都需要大量的光纖連接。這就要求PIC中的關鍵電路小型化,尤其是調製器,通常採用微環調製器,而不是可插拔光器件中使用的體積更大的馬赫-曾德爾調製器。橫向擴展轉向CPO的原因是,其功耗比可插拔光器件低2/3:網絡傳輸中節省的每一瓦功耗都可以用於計算,從而帶來收益。

台積電目前幾乎為英偉達、AMD、谷歌、AWS 等公司生產所有 AI 加速芯片。這些芯片由衆多芯片組(GPU/XPU、HBM、I/O)組成。台積電要求封裝內的所有芯片組都必須由台積電按照其PDK(工藝開發套件)和規範生產,以確保正常運行和高良率。這意味着台積電集成的所有硅光子芯片組都將由台積電生產。一段時間以來,台積電一直在開發其COUPE工藝。很可能,他們開發這項工藝是為了響應其最大客戶英偉達和博通的需求,這兩家公司都已於去年開始在其橫向擴展交換機中部署 COUPE 工藝。

鑑於 a) 硅光子晶圓代工收入增長 8 倍需要鉅額資本支出; b) 台積電目前生產 AI 加速器中所有非 HBM 芯片,未來五年內,隨着 AI 加速器向 CPO 過渡,台積電很可能從硅光子領域的零基礎躍升為全球第一的硅光子晶圓代工廠。日月光等公司擁有一定的 CoWoS 產能,因此可能會出現一些非台積電生產的有機襯底 CPO 產品。或者,格芯或其主要客戶可能會說服台積電使用格芯製造的光學引擎芯片——格芯目前最先進的製程節點為 12nm,因此在 AI 加速器領域對台積電並不構成競爭威脅。

硅光子器件、設計和芯片

CMOS 設計師通常會使用包含大量規則和公式的 1000 頁 PDK(產品開發工具包)。這些 PDK 包括代工廠提供的多個器件庫(只要遵循這些規則,這些器件就能協同工作),以及許多構成完整子系統的大型複雜 IP(知識產權)。

如今的硅光子學就像上世紀80年代的硅設計一樣,當時晶圓廠的文檔有限,只能用環形振盪器來展示性能,設計人員必須自行構建器件庫,並從SPICE開始進行建模。硅光子學的蓬勃發展,以及台積電進軍硅光子學領域,有望在未來五年內帶來更多結構和基礎知識產權。像Synopsys和Cadence這樣的公司確實提供硅光子學設計工具,但設計人員正在開發的許多結構都是全新的,需要從基礎物理原理出發進行非常詳細、耗時的底層建模。

圖 9:光子集成電路平台的典型庫組件:生成、路由、處理、檢測和調製

硅光子器件採用 200 毫米和 300 毫米晶圓製造,工藝精度可達 65 納米。所用晶圓為 SOI 結構,並帶有至少 1 微米厚的埋氧層(BOX:SiO2),用於光隔離。如下圖所示,這是因為在硅(或氮化硅)波導中傳輸的單模光主要在硅波導芯內傳播,但部分光場會「泄漏」到上方、側面和下方的相鄰材料中。因此,這些層必須足夠厚,以防止光傳播到其他有源區域。

圖 10:波導中的單模光「泄漏」到周圍材料中

硅光子學的一大挑戰是信號損耗——波導輸入端的信號強度會隨着波導中每單位距離的傳輸而損耗。所有光器件都會產生信號損耗。如果信號損耗累積過高,信號強度將不足以正常工作。因此,在硅光子學設計中,對信號損耗的精確控制至關重要。

在硅光子學中,通常不使用CMOS晶體管(硅光子學和CMOS的集成已經開始——GF公司有一種將兩者結合起來的工藝——但目前還不普遍)。硅光子學工藝中通常可用的器件包括:

1、佈線:波導,由硅和氮化硅製成。波導需要一定的高度和寬度才能保證光的單模傳輸,並且波導周圍需要有足夠的材料,以防止光與其他元件發生相互作用。波導不能以90度角急轉彎。彎曲需要一定的最小半徑,以確保光在波導內發生折射。有趣的是,兩個波導可以垂直交叉,且垂直光束之間的相互作用極小。這一點非常重要,因為許多代工廠只生產單層波導。

2、檢測:檢測分為兩類:耦合器和光電探測器。耦合器用於捕獲從光纖進入芯片的光。將光耦合到芯片的最有效方法是使用邊緣耦合器,但光纖和芯片的對準可能具有挑戰性。將光纖對準芯片以進行耦合的最簡單方法是從上方使用光柵耦合器。一維光柵耦合器用於偏振光,二維光柵耦合器用於非偏振光。偏振光纖比標準單模光纖 (SMF) 貴得多,因此通常僅用於激光器到芯片的連接——激光器通過信號損耗較低的一維光柵耦合器連接到芯片。二維光柵耦合器可以捕獲非偏振光,但體積更大、結構更復雜,並且信號損耗更大。它們用於數據信號。光電探測器用於將波導中的光強度轉換為可由配套 CMOS 芯片讀取的電信號。光電探測器採用鍺製造,而鍺並不是CMOS製造廠的常用材料。

3、調製:調製器用於將電信號轉換到光信號上。在可插拔光器件中,調製器是馬赫-曾德爾調製器。在CPO(耦合光子器件)中,調製器是微環,它是一種尺寸小得多的器件,對於縮小CPO芯片的尺寸至關重要,因為CPO芯片需要將數十根光纖集成到狹小的空間內,以便與GPU耦合。如下圖所示,加熱器用於控制調製器,根據來自配套CMOS芯片的電信號,將比特插入到輸入的激光束中。在高速傳輸時,這需要高速PHY來驅動調製器。機械應力和電壓也可以用作光子器件的控制手段。

4、處理方法:採用干涉儀配置的馬赫-曾德爾器件可用於構建光開關,該開關接收兩束入射光並分別輸出兩束光。通過控制加熱器,該開關可以配置為輸入0輸出0、輸入1輸出1,或者輸入0輸出1、輸入1輸出0。這些開關的切換速度可達微秒級。

圖 11:AMF(現為 GF)標準 MPW(多項目晶圓)流程的橫截面視圖

上圖所示的氧化物窗口用於生物/化學光子傳感器,使其能夠與光場相互作用。這並非數據中心的應用。

通常,硅光子芯片不包含CMOS器件。與CMOS晶體管相比,光子器件的物理尺寸較大。例如,CMOS和SiPho芯片採用45nm工藝。儘管某些光子器件特性可以受益於先進的光刻技術,但光子技術短期內(甚至可能永遠)都無法集成到3nm或2nm工藝中。

圖 12:硅光子芯片的示意圖和芯片照片

總結

利用硅光子技術,現在可以製造出能夠對光進行復雜操控的芯片。如上圖所示,這些結構體積龐大,類似於早期的CMOS工藝。硅光子技術在數據中心的主要功能是在高性能CMOS計算芯片和交換機之間,以及可能還有內存池之間進行數據傳輸。這些硅光子芯片將越來越多地集成到數據中心的每個單元中,我們將很快習慣於看到帶有明亮黃色光纖的電路板,這些光纖傳輸着高帶寬數據。服務器微處理器很可能也會採用這種技術,用光學器件取代PCIe(外圍組件互連) 。

硅光子製造的產業結構也將發生類似的變革,晶圓收入將實現數量級增長,台積電有望憑藉其在人工智能加速器(包括光引擎在內的所有芯片組件)製造中的作用,成為最大的供應商。台積電可能會像在CMOS領域一樣,將許多架構和基礎設施引入硅光子領域,從而以更短的時間和更低的成本開發出更復雜的光子芯片。

若您對硅光SiGe技術及流片相關話題有更多探討需求,歡迎添加微信深入交流。