最近,苹果公司新发布了一项名为“具有高动态范围和低噪点的堆叠像素图像传感器”的专利。这项发现可能预示着一项可能重塑移动和专业成像领域的突破。苹果公司声称其堆叠式传感器架构拥有高达20档的动态范围,或许正蓄势待发,准备与电影摄影机技术领域的巨头们竞争,甚至超越他们。

一、性能超越最佳的传感器

苹果新发布的一项名为“高动态范围低噪点堆叠像素图像传感器”的专利,揭示了成像技术的重大进步。虽然苹果以其定制芯片和相机软件而闻名,但这项专利暗示着一项更具雄心的目标:一种完全自主设计的图像传感器,其动态范围有望与领先的电影摄影机相媲美,甚至超越它们。而且,这并非仅仅是理论上的——该传感器架构声称其动态范围高达120 dB,相当于近20档的动态范围。这比目前业界的巨头,例如ARRI ALEXA 35,都要高得多。

按照苹果在专利描述文件中所说:

本文描述的本发明实施例提供了一种包含新颖设计的3T像素的图像传感器,该传感器可实现高动态范围、低噪声,并且不会出现传统4T像素阵列中可能出现的伪影。该图像传感器包含一个堆叠在逻辑芯片上的传感器芯片。每个3T像素在传感器芯片上包含一个传感电路,该电路包括一个光电二极管和一个横向溢流积分电容(LOFIC:lateral overflow integration capacitor)电路,以便在从室内到明亮阳光的各种光照条件下进行传感,而无需自动曝光控制。

此外,每个像素在逻辑芯片上包含一个像素电路,该电路包含一个电流存储电路。该电流存储电路用于感测探测器元件中的噪声水平。电流存储电路输出的信号能够利用CDS抑制热噪声(kTC)。

二、苹果的专利内容是什么?

该专利概述了一种由两层组成的堆叠传感器:传感器芯片(带有光电二极管和模拟电路)和逻辑芯片(处理读出、噪声消除和控制)。

这种堆叠式方法与索尼的做法类似,使苹果能够将先进的电路封装到更薄的传感器模块中,非常适合智能手机和Vision Pro等AR/VR设备。但真正的创新在于像素级架构,其特点如下:

1. LOFIC(横向溢流积分电容器)

这种机制使传感器能够处理三个电荷存储层级的光溢出,自动适应极端亮度或黑暗环境——一次性完成。这便是20档动态范围得以实现的原因。

2. 内置噪声感应电路

每个像素内的电流存储电路可实时检测并消除热噪声,这意味着即使在低光照条件下,最终图像也更加清晰-无需后期处理或AI技巧。

3. 3T像素设计(非4T)

令人惊讶的是,苹果采用了3晶体管设计,这种设计通常被认为更简单,但噪音也更大。然而,得益于上述创新,该设计比标准的4T传感器噪音更低,从而以更少的组件和更高的效率提供更佳的性能。

按照苹果所说:

本例中的LOFIC电路44包括两个电荷存储电容器50和52以及两个串联连接到浮动扩散节点42的LOFIC晶体管(LOFIC1和LOFIC2)54和56。第一个LOFIC晶体管(LOFIC1)54将浮动扩散节点连接到第一个电荷存储电容器50的电荷输入端,该电容器的电容较小,例如约为20 fF。第二个LOFIC晶体管56将第一个电荷存储电容器50的电荷输入端连接到第二个电荷存储电容器52的电荷输入端,该电容器的电容较大,例如约为500 fF。

在此配置中,浮动扩散节点42本身将用于在弱光条件下存储和读出光电荷;电荷存储电容器50将用于在中等光照条件下存储和读出光电荷;电荷存储电容器52将用于在强光条件下存储和读出光电荷。这种LOFIC结构使探测器元件26能够感测约120 dB动态范围内的光。或者,也可以使用其他LOFIC结构,并采用更少或更多数量的电容器和晶体管。

三、这个产品意味着什么?

如果这项技术得以实施(或许在未来的iPhone 17 Pro或Apple Vision Pro 2中),它可能会导致:

移动设备上的电影级HDR;

实时无噪音视频捕捉;

超薄外形,专业品质成像,具有极高的DR(20档动态范围)。

苹果可能正准备摆脱对索尼高端相机传感器的依赖,以竞争对手而非客户的身份进入图像传感器市场。这也表明,苹果在计算摄影领域的下一次飞跃可能植根于以图像传感器为先的创新,而非软件或人工智能。

动态范围和噪点是数字成像的两个主要制约因素。一款能够提供20档动态范围和先进片上噪点抑制功能的移动式或紧凑型传感器,不仅是一种改进,更是颠覆性的。

这可能会影响:

移动电影摄影;

HDR流媒体内容;

AR/VR视觉保真度;

即使是专业的电影制作套件,紧凑性和质量也必须共存。

由于这是苹果公司的产品,因此不难想象该公司会将该传感器与神经引擎处理深度集成,使其在极端条件下更加强大。

在我们看来,这项专利目前可能不太引人注目,但其影响深远。苹果不仅仅是在改进相机软件,而是从芯片层面重新定义图像传感器。如果这项技术投入生产,我们可能会看到数字成像领域的全新黄金标准——不仅在智能手机领域,也在电影领域。

四、具有高动态范围和低噪声的堆叠像素图像传感器

目前使用的绝大多数图像传感器都是CMOS(互补金属氧化物半导体)有源像素传感器(APS)单片阵列,具有4T像素。在这些器件中,每个探测器元件(称为“像素”)包含一个光电二极管、一个浮动扩散区和四个CMOS晶体管,其中包括一个传输门、一个复位门、一个选择门和一个源极跟随器读出晶体管。传输门控制从光电二极管到浮动扩散区的电荷转移,并通过相关双采样(CDS)实现降噪。使用3T像素(没有传输门)的图像传感器更容易制造,也更不容易出现伪影,但通常噪声较高。

概括:

下文描述的本发明实施例提供了改进的图像传感器以及用于生产和控制此类图像传感器的方法。

因此,根据本发明的一个实施例,提供了一种图像传感器,该图像传感器包括一个逻辑芯片,该逻辑芯片包含列读出电路和连接到列读出电路的位线,以及一个覆盖在逻辑芯片上的传感器芯片。该图像传感器包括一个探测器元件阵列,每个探测器元件包括一个设置在传感器芯片上的传感电路和一个设置在逻辑芯片上的像素电路。

该传感电路包括一个具有阴极和阳极端子的光电二极管、一个连接到光电二极管其中一个端子的浮动扩散节点、一个耦合在浮动扩散节点和复位电压之间的复位晶体管,以及一个具有连接到浮动扩散节点的输入和输出的源极跟随器晶体管。

像素电路包括一个选择晶体管,该选择晶体管具有耦合到源极跟随器的输出的输入和耦合到其中一条位线的输出,以及一个电流存储器电路,该电流存储器电路耦合到选择晶体管的输入,并配置为感测和输出指示检测器元件中的噪声水平的信号。

在一些实施例中,每个感测电路包括一个横向溢流积分电容(LOFIC)电路,该电路包括一个或多个电荷存储电容以及耦合在浮动扩散节点和电荷存储电容之间的一个或多个LOFIC晶体管,其中,复位晶体管耦合在LOFIC电路和复位电压之间。

在一个公开的实施例中,该LOFIC电路包括:具有第一电容的第一电荷存储电容;具有大于第一电容的第二电容的第二电荷存储电容;连接在浮动扩散节点和第一电荷存储电容的第一电荷输入端之间的第一LOFIC晶体管;以及连接在第一电荷存储电容的第一电荷输入端和第二电荷存储电容的第二电荷输入端之间的第二LOFIC晶体管。

在一个实施例中,复位晶体管连接在第二电荷存储电容的第二电荷输入端和复位电压之间。此外或可选地,在将检测器元件读出到位线期间,第一和第二LOFIC晶体管依次导通,同时选择晶体管导通。

在一些实施例中,在每个图像帧期间,复位晶体管在第一复位周期内导通,以在帧的曝光周期之前复位浮动扩散节点;选择晶体管在曝光周期之后的第一读出周期内导通,以从浮动扩散节点读出光电荷。然后,复位晶体管在第一选择周期之后的第二复位周期内导通,以复位浮动扩散节点;选择晶体管在第二复位周期之后的第二读出周期内导通,以读出探测器元件累积的噪声。

在一些实施例中,电流存储电路包括至少一个采样电容器和至少一个采样晶体管,它们耦合在选择晶体管的输入端和至少一个采样电容器之间,其中,至少一个采样晶体管在第一和第二复位周期内跟随复位晶体管导通,使得至少一个采样电容器对探测器元件中的kTC噪声进行采样。

在公开的实施例中,电流存储电路包括:连接在选择晶体管的输入端和至少一个采样晶体管之间的读取晶体管;以及与读取晶体管并联的、极性与读取晶体管相反的偏置晶体管。其中,读取晶体管和偏置晶体管在第一和第二读出周期导通,在曝光周期截止。在一个实施例中,偏置晶体管在第一和第二复位周期导通。

另外或可替代地,至少一个采样电容器包括第一和第二采样电容器,并且至少一个采样晶体管包括第一和第二采样晶体管,它们串联耦合在第一和第二采样电容器与选择晶体管的输入端之间。

根据本发明的一个实施例,还提供了一种图像感测方法,该方法包括:提供一个逻辑芯片,该逻辑芯片包括列读出电路和连接到列读出电路的位线;以及在逻辑芯片上覆盖一个传感器芯片。在传感器芯片和逻辑芯片上形成一个探测器元件阵列,每个探测器元件包括一个形成在传感器芯片上的感测电路和一个形成在逻辑芯片上的像素电路。

每个感测电路包括一个具有阴极和阳极端子的光电二极管、一个连接到光电二极管其中一个端子的浮动扩散节点、一个耦合在浮动扩散节点和复位电压之间的复位晶体管,以及一个具有连接到浮动扩散节点的输入和输出的源极跟随器晶体管。

每个像素电路包括一个选择晶体管,该选择晶体管具有耦合到源极跟随器的输出的输入和耦合到其中一条位线的输出,以及一个电流存储器电路,该电流存储器电路耦合到选择晶体管的输入并配置为感测和输出指示检测器元件中的噪声水平的信号。

通过以下结合附图对本发明实施例的详细描述,将更全面地理解本发明:

实施例详细说明

本文描述的本发明实施例提供了一种包含新颖设计的3T像素的图像传感器,该传感器可实现高动态范围、低噪声,并且不会出现传统4T像素阵列中可能出现的伪影。该图像传感器包含一个堆叠在逻辑芯片上的传感器芯片。

每个3T像素在传感器芯片上包含一个传感电路,该电路包括一个光电二极管和一个横向溢流积分电容(LOFIC)电路,以便在从室内到明亮阳光的各种光照条件下进行传感,而无需自动曝光控制。此外,每个像素在逻辑芯片上包含一个像素电路,该像素电路包含一个电流存储电路。该电流存储电路用于感测探测器元件中的噪声水平。电流存储电路输出的信号能够利用CDS抑制热噪声(kTC)。

虽然逻辑芯片上的电流存储电路与LOFIC电路配合使用特别有用,但在其他实施例中,即使没有LOFIC电路,逻辑芯片上的组件也可用于降低其他图像传感器像素中的噪声。

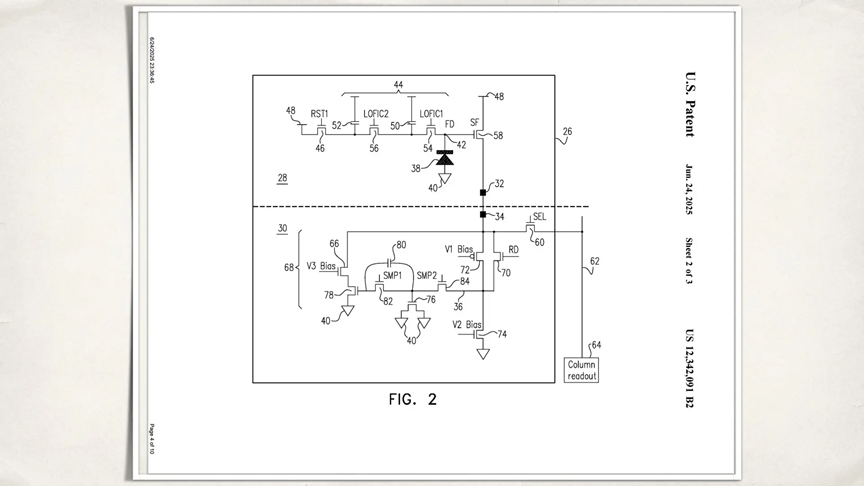

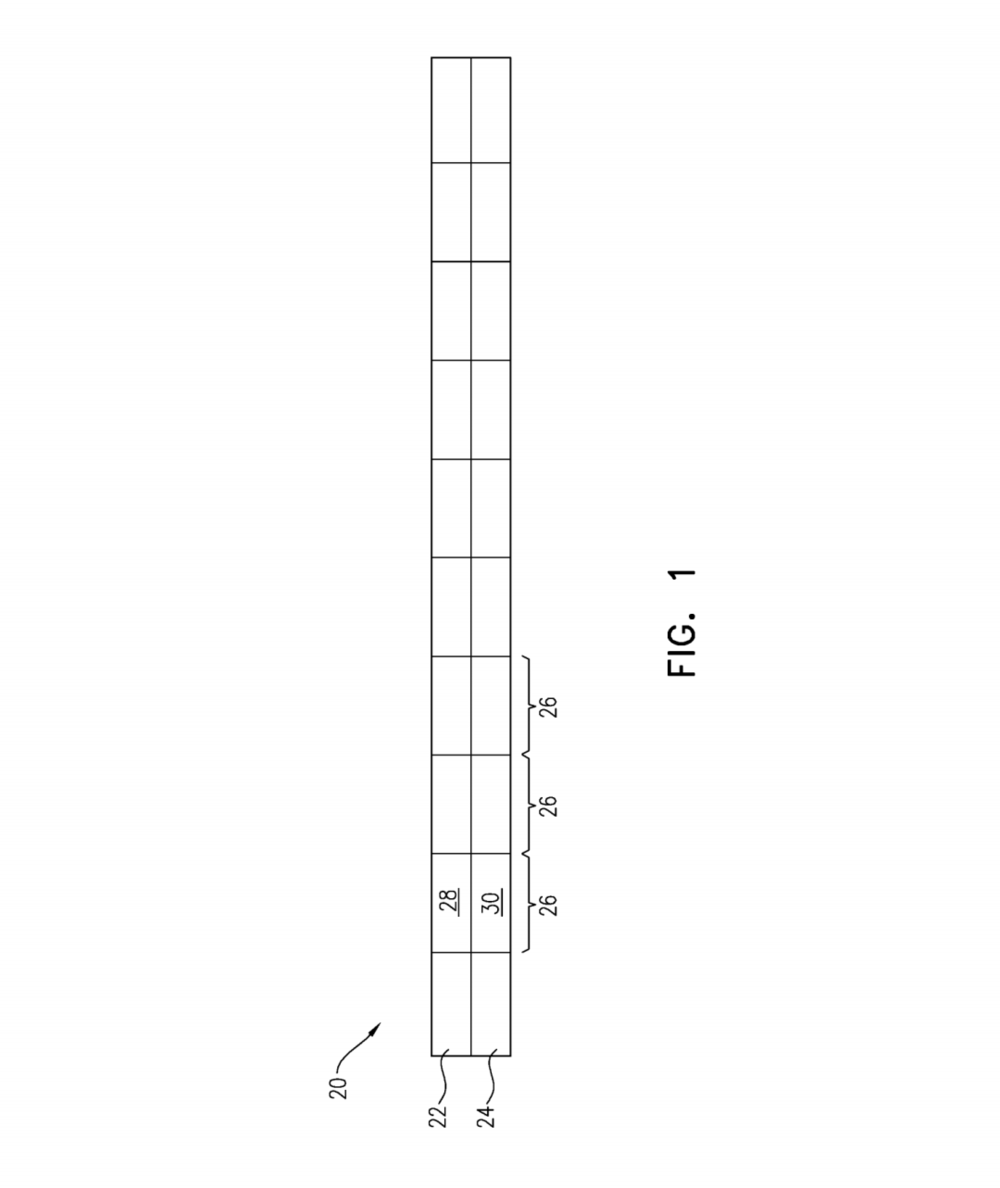

图1是根据本发明实施例的图像传感器的示意侧视图;

图1是根据本发明实施例的图像传感器20的示意侧视图。图像传感器20包括由一个硅芯片制成的逻辑芯片24,以及由另一个硅片制成的传感器芯片22,该芯片覆盖在逻辑芯片24上。图像传感器20包含一个探测器元件阵列26(也称为像素),每个探测器元件包括位于传感器芯片22上的传感电路28和位于逻辑芯片24上的像素电路30。像素电路30通过位线连接到列读出电路(如图2所示)。图像传感器20的堆叠硅片配置使得在逻辑芯片24中使用标准CMOS控制和读出电路成为可能,而传感电路28可以通过不同的工艺制造。或者,传感器芯片22可以包含除硅之外的其他半导体材料。

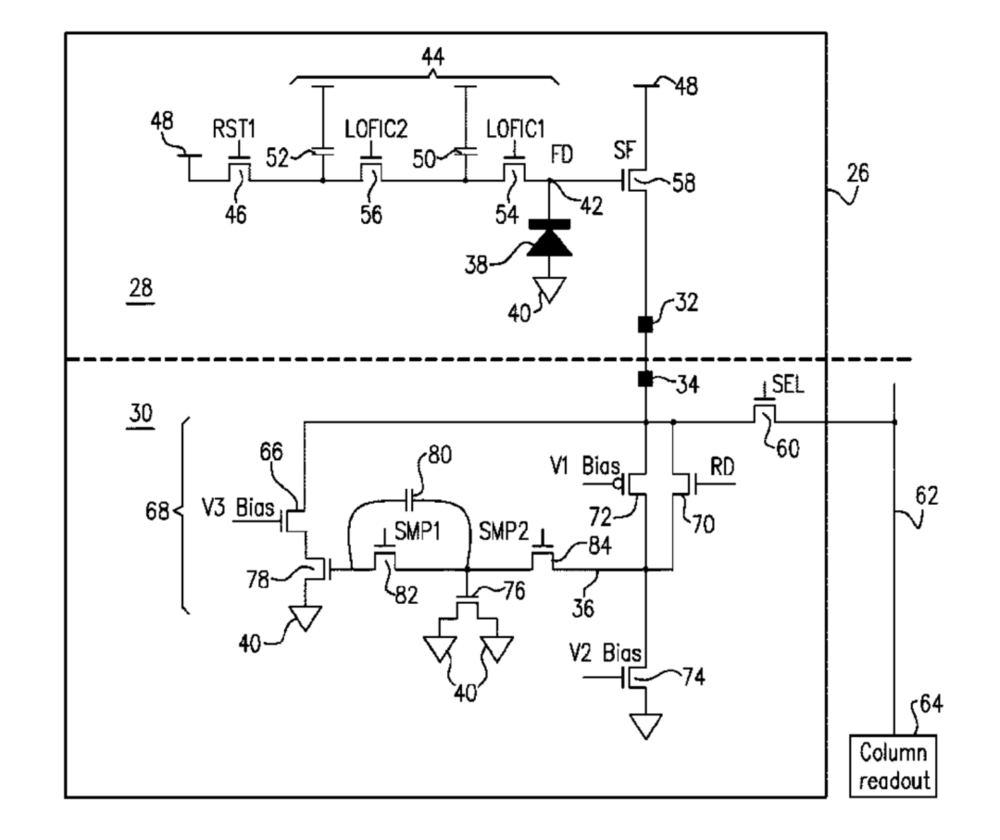

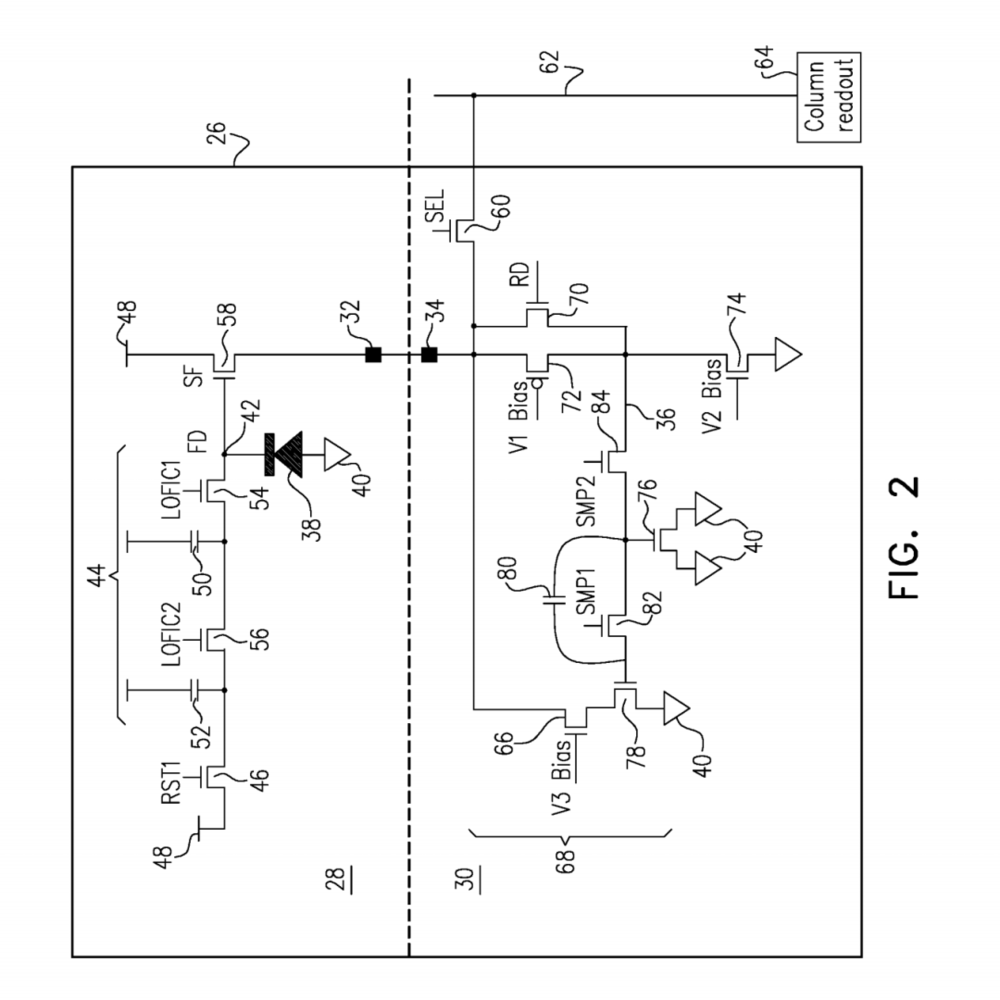

图2是根据本发明实施例的图像传感器中探测器元件细节的示意电路图;

图2是根据本发明实施例的探测器元件26之一的示意电路图。图2中所示的传感电路28包含N沟道MOSFET晶体管和N-on-P光电二极管38。或者,传感电路28也可以包含P沟道晶体管和P-on-N光电二极管。传感电路28的组件连接到电源电压48,例如1.5 V、1.2 V或1.0 V。在本设计中,无需将电压升压至高于电源电压或低于地电位。

传感电路28包含一个浮动扩散节点(FD:floating diffusion)42,该节点连接到光电二极管38的一个端子(在本例中连接到阴极,阳极连接到地40)。横向溢流积分电容(LO-FIC)电路44耦合至浮动扩散节点42,复位晶体管(RST1)46耦合于LOFIC电路和复位电压(在图示示例中,该复位电压为电源电压48)之间。

本示例中的LOFIC电路44包括两个电荷存储电容器50和52,以及两个串联耦合至浮动扩散节点42的LOFIC晶体管(LOFIC1和LOFIC2)54和56。第一个LOFIC晶体管(LOFIC1)54将浮动扩散节点连接到第一个电荷存储电容器50的电荷输入端,该电容器具有较小的电容,例如约为20 fF。

第二个LOFIC晶体管56将第一个电荷存储电容器50的电荷输入端连接到第二个电荷存储电容器52的电荷输入端,该电容器具有较大的电容,例如约为500 fF。在该配置中,浮动扩散节点42本身将用于在弱光条件下存储和读出光电荷;电荷存储电容器50将用于在中等光照条件下存储和读出光电荷;电荷存储电容器52将用于在强光条件下存储和读出光电荷。该LOFIC配置使探测器元件26能够感测约120 dB动态范围内的光。或者,也可以使用其他LOFIC配置,其中电容器和晶体管的数量可以更少或更多。

源极跟随器晶体管(SF:source follower transistor)58的栅极连接用于接收来自浮动扩散节点42的电荷输入,其漏极连接到输出端子32,该输出端子与像素电路30的输入端子34连接。输入端子34连接到选择晶体管(SEL)60。当选择晶体管导通时,它会将来自探测器元件26的信号输出到位线62,该位线为探测器元件阵列的提供服务。

如上所述,该位线将传感器芯片22中的探测器元件连接到逻辑芯片24中的列读出电路64。在从探测器元件26读出数据期间,连接到输入端子34的偏置晶体管(V3 Bias)66处于关闭状态,通常消耗约1 uA的电流。

为了实现噪声感测和消除,像素电路30包含一个电流存储电路68,该电路包含一个N沟道读取晶体管(RD:read transistor)70和一个P沟道偏置晶体管(V1 Bias)72并联。本例中的读取晶体管和偏置晶体管极性相反。因此,在图示的示例中,读取晶体管70(以及像素电路30的其他组件)是N沟道器件,而V1 Bias晶体管72是P沟道器件。第二个偏置晶体管(V2 Bias)74与P沟道偏置晶体管串联,当两个偏置晶体管导通时,会吸收偏置电流,例如约100 nA。

采样线36连接到读取晶体管70和V1偏置晶体管72的漏极以及V2偏置晶体管74的源极。从检测器元件26流出的电流由一对采样电容器76、78采样,这对采样电容器连接在采样线36和地40之间。这些采样电容器76、78可以具有低电容,例如每个约为4 fF,并且两个采样电容器之间存在大约0.1 fF的附加寄生耦合80。

为了在感测电路复位期间对流经感测电路28的电流进行采样,一对采样晶体管(SMP1和SMP2)82、84会短暂地同时导通。然后,晶体管82(SMP1)关闭,接着晶体管84(SMP2)也关闭。晶体管82对探测器元件26的kTC噪声进行采样,而晶体管84对晶体管82关闭后的残余误差进行采样。因此,kTC噪声被采样,并通过流入和流出采样电容器78的电流进行补偿。

在从探测器元件26读出期间,采样的电流信号由选择晶体管60读出到位线62。或者,电流存储电路68可以仅包含一个采样电容器,也可以包含更多数量的采样电容器,并相应地布置一个或多个采样晶体管。

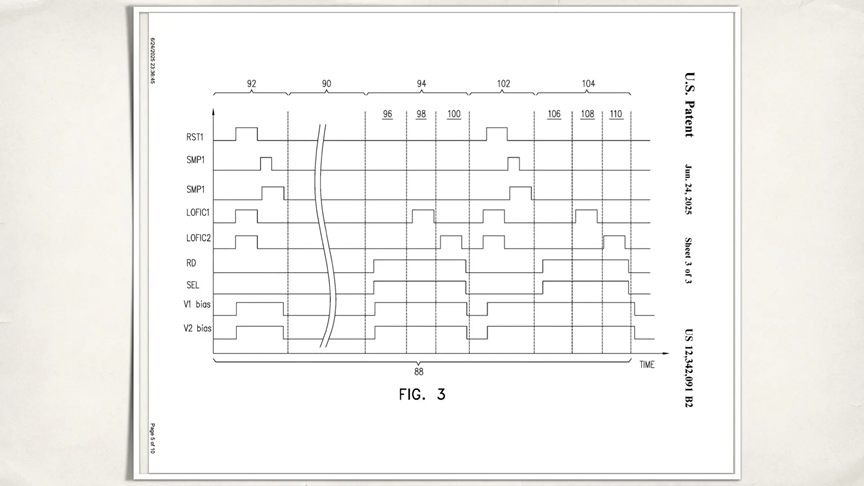

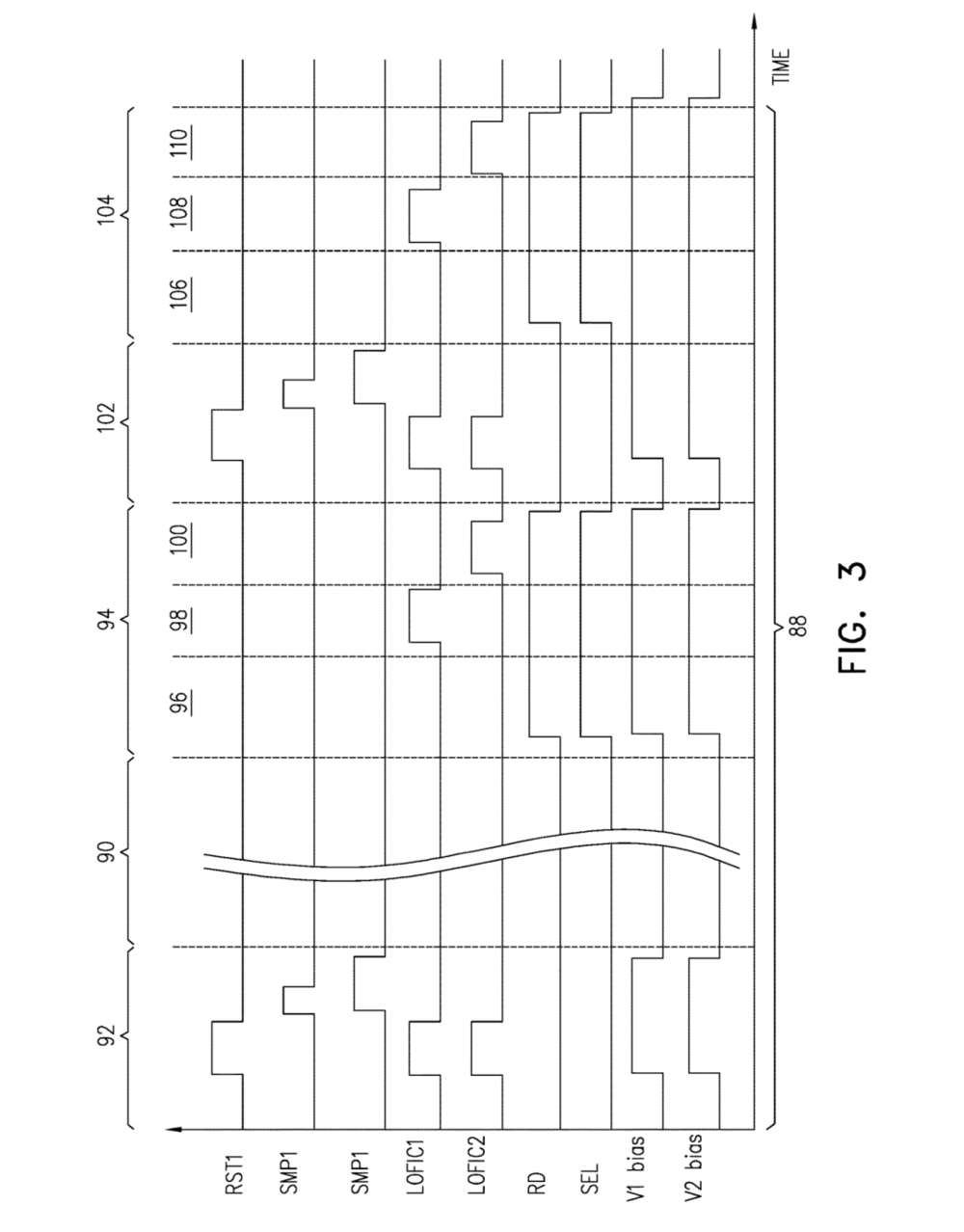

图3是根据本发明实施例的时序图,示意性地示出了施加到图2中探测器元件晶体管的信号

图3为时序图,示意性地示出了根据本发明实施例的在单个图像帧88过程中施加到探测器元件26的晶体管46、54、56、66、70、72、74、82和84的信号。为了简化说明,施加到晶体管72的V1偏置信号显示为与其他信号具有相同的极性;但实际上,由于V1偏置晶体管72是P沟道器件,因此V1偏置信号的极性将与其他信号的极性相反。施加到晶体管66的V3偏置信号与V2偏置信号相同,因此为了简单起见,此处省略。

每个图像帧88包括曝光期90,例如在1-10毫秒的范围内,在此期间,来自光电二极管的光电荷在浮动扩散节点42处收集,并且可能在LOFIC电荷存储电容器50、52中的一个或两个上收集,具体取决于入射光的强度。在曝光期90之前的预曝光复位期92中,复位晶体管(RST1)46导通,以复位浮动扩散节点42。LOFIC晶体管54、56也与RST1一起导通,以复位LOFIC电荷存储电容器50、52。

此外,在曝光期之前的复位期内,像素电路30中的偏置晶体管72、74、66(V1 Bias、V2 Bias和V3 Bias)均导通,采样晶体管82、84(SMP1和SMP2)在RST1复位脉冲之后导通,然后依次关闭。

在曝光周期90之后,选择晶体管60和读取晶体管70(SEL和RD)在读出周期94期间导通,同时三个偏置晶体管72、74和66(V1 Bias、V2 Bias和V3 Bias)也导通,以将光电荷从浮动扩散节点42读出到位线62。读出周期94包括高增益间隔96、中增益间隔98和低增益间隔100。当选择晶体管60导通时,浮动扩散节点42上的电荷首先在高增益间隔96期间被读出。然后,LOFIC晶体管54和56依次在中增益间隔98和低增益间隔100期间导通,以将存储在LOFIC电荷存储电容器50和52中的光电荷读出到位线62。

所有光电荷读出后,复位晶体管在曝光后复位周期102中,(RST1)46与两个LOFIC晶体管54、56再次导通,以复位浮动扩散节点42和LOFIC电荷存储电容器54、56。像素电路30中的偏置晶体管72、74、66(V1 Bias、V2 Bias和V3 Bias)再次全部导通,采样晶体管82、84(SMP1和SMP2)在RST1复位脉冲后导通,然后依次关断,就像在复位周期92期间一样。

在这些复位之后,选择晶体管60和读取晶体管70在噪声读出周期104期间再次导通,以读出探测器元件26积累的噪声。噪声读出周期104包括高增益间隔106、随后的中增益间隔108和低增益间隔110。当选择晶体管60和读取晶体管70导通时,浮动扩散节点42上的电荷首先在高增益间隔106期间被读出。然后,LOFIC晶体管54和56依次在中增益间隔108和低增益间隔110期间导通,以将LOFIC电荷存储电容器52和54中剩余的电荷读出到位线62。

在噪声读出周期104期间,偏置晶体管72、74和66保持导通。电流存储电路68感测并输出指示探测器元件26中噪声水平的信号。逻辑芯片24中的CDS电路(未示出)从曝光周期后读出的光信号中减去在此第二读出周期读出的噪声信号,从而降低图像传感器20输出信号中的噪声影响。

应当理解,上述实施例仅作为示例引用,本发明不限于上述具体显示和描述的内容。相反,本发明的范围包括上述各种特征的组合和子组合,以及本领域技术人员在阅读前述说明后能够想到的、且在现有技术中未公开的变体和修改。