炒股就看金麒麟分析师研报,权威,专业,及时,全面,助您挖掘潜力主题机会!

(来源:爱集微)

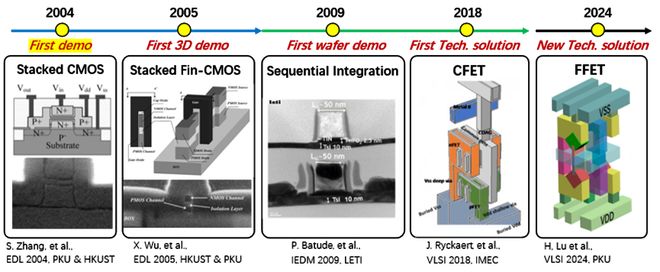

三维晶体管结构包括FinFET和GAA FET等,是半导体工艺演进中的关键性突破之一,其重要性在于解决了传统平面晶体管在纳米尺度下的物理极限问题,支撑了摩尔定律的延续。2011年,英特尔成功量产采用FinFET的处理器;2022年,三星电子成为全球首家在3纳米工艺中量产采用GAA结构的逻辑半导体的公司;2025年,台积电将量产2纳米工艺,采用GAA结构。这些都有效推进了半导体技术工艺的演进发展。而在第42届超大规模集成电路研讨会(VLSI 2025)上,北京大学微电子学院黄如院士团队公布了新一代三维晶体管结构“倒装堆叠晶体管(Flip FET, FFET)”,首次实现了8层晶体管的三维垂直集成,单位面积逻辑密度较传统FinFET提升3.2倍,功耗降低58%。这一突破性成果被业界视为延续摩尔定律的最具潜力方案之一。

三维晶体管技术持续演进

受人工智能、高性能计算、数据中心等应用的推动,近年来半导体先进逻辑工艺的市场规模不断扩大,直接推动了全球半导体产业的成长。市调机构Counterpoint Research最新报告显示,全球纯半导体晶圆代工行业收入预计在2025年将同比增长17%,超过1650亿美元。先进的3nm和5/4nm节点在推动半导体收入增长方面发挥着关键作用,预计2025年3nm节点的收入将同比增长超过600%,达到约300亿美元;包括 7nm在内的先进节点将在2025年贡献纯晶圆厂总收入的一半以上。

然而在技术层面,传统的二维平面集成方式面临物理极限和工艺极限的瓶颈,当晶体管尺寸缩小至20nm以下时,栅极对沟道的控制力减弱,导致漏电流剧增、功耗失控,三维堆叠成为接续摩尔定律演进的主要方向。

从目前业界的发展进程来看,FinFET解决平面晶体管失效问题,在10年内支撑了从16nm到5nm的跨越。3nm/2nm以下GAA 将接棒,确保芯片在功耗、性能、集成度上的持续进步。三星电子2022年首家量产采用GAA结构的3纳米工艺;2025年台积电将采用GAA量产2nm工艺,同时计划在2027年后推出N2P、N2X等2nm的变体工艺,进一步优化性能与功耗。

至于再下一代的三维晶体管结构,IMEC于2018年提出的补场效应晶体管(Complementary FET, CFET)被认为是一个有力的竞争者。根据此前IMEC公布的技术路线图,凭借CFET,芯片工艺技术在2032年将有望进化到5埃米(0.5nm),2036年有望实现2埃米(0.2nm)。台积电、三星、英特尔等都在实验室中对CFET进行了预研开发。

北大 Flip FET 实现架构创新

不过随着近年来在半导体技术研发投入上的增加,我国在新一代三维晶体管结构上也开始发出自己的声音。北京大学吴恒研究员-黄如院士团队在2024年6月召开的集成电路顶级会议VLSI2024上,首次提出了FlipFET技术。在今年召开的VLSI2025上,北大团队再次发布相关研究成果。根据北京大学集成电路学院发布的消息,在VLSI2025上北京大学集成电路学院共有12篇高水平学术论文入选。其中“倒装堆叠晶体管的高密度集成验证”和“面向亚1nm节点的倒装堆叠晶体管演进路线图”,都受到极大关注。

根据相关报道,在3D堆叠晶体管和背面互连技术等新型架构的开发过程中,面临着高深宽比工艺难点以及设计复杂性等挑战。FlipFET通过自对准地背靠背堆叠正面(FS)NFET和背面(BS)PFET,并结合双面电源/信号互连,可实现高密度的晶体管和互连线集成。在此基础上,为获得完整晶圆级集成结果,经过一年多的打磨,北京大学吴恒研究员-黄如教授团队开发了一系列关键工艺模块,包括晶圆键合、衬底减薄、背面沟道形貌优化以及背面光刻对准校正,成功获得了FlipFET的关键正反面器件电性,并报道了世界首个背部集成的逻辑晶体管技术。

实验结果表明,正面NFET经过翻转表现良好,背面PFET性能优异(最小沟长低至30 nm,SS=73.1 mV/dec,DIBL=24 mV,开关比达107),与正面NFET相当。FlipFET还展现出天然分离栅结构、约500 mV的多阈值电压可调性以及实现双面CMOS的能力,显著优于传统的单片CFET。这些进展验证了FlipFET在工艺可实现性、设计灵活性和可扩展性方面的巨大潜力,使其成为超越1nm逻辑节点的重要候选技术。

在面向亚1nm节点的倒装堆叠晶体管演进路线图的研究中,北大团队针对A2及以下工艺节点面临的功耗、性能与面积(PPA)挑战,提出了三代结构创新:1)完全自对准倒装堆叠晶体管F3ET,实现正反面栅极的自对准,提高设计灵活性并降低栅极互连电阻;2)基于叉形晶体管的完全自对准倒装堆叠晶体管F4ET,并结合嵌入式供电轨(embedded Power Rail)及背面接触(Backside Contact),实现了极致2T标准单元设计;3)基于互补堆叠晶体管的倒装堆叠晶体管CFFET,实现四层晶体管的终极堆叠。

同时,研究还拓展至SRAM的微缩路径,基于多种倒装堆叠SRAM架构方案,成功实现了FFET SRAM在A2节点下的同步缩放。该研究构建出一套面向极限尺度的DTCO优化路径,验证了FFET面向亚1nm先进逻辑晶体管微缩的潜力。

CFET与中国Flip FET的技术探索

就半导体工艺技术而言,所有的现代计算机芯片都是由晶体管组成的。经典的平面晶体管结构都包含一个栅极、一个源极和一个漏极,并排列在一个二维平面上。当人们对栅极施加一个电压,栅极就会打开,电流从源极流向漏极,电路就会导通。这是现代计算机芯片最基础的结构。但随着晶体管的尺寸不断缩小,特别是沟道的尺寸也随之缩小,人们面临的问题也随之增加,人们的解决方案是改变晶体管的结构。从二维平面变为三维立体,从FinFET、GAA到CFET以及Flip FET,目标都是提高晶体管密度,改善高漏电等问题。

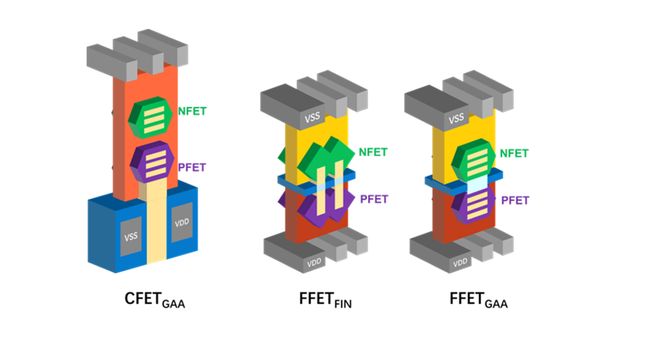

CFET的目的就是在单一集成工艺中将n型(nFET)和p型(pFET)晶体管堆叠在一起,通过晶体管级的三维堆叠集成,在晶体管结构上作出改变,以便更高效地利用空间,提升器件密度和性能。

据芯思想报道,晶体管级的三维集成技术目前已经受到广泛关注。其设计思路是通过在垂直方向上堆叠器件和互连,将传统的单面布局扩展至多面空间,在掩模版尺寸受限的条件下为单芯片提供了突破集成密度上限的可能。

相较而言,CFET的核心是将n型和p型晶体管纵向堆叠于同一单元内,直接压缩水平面积。Flip FET则是在晶圆正面制作nFET,背面制作pFET,通过晶圆翻转实现双面器件堆叠。结合背面电源轨(BPR)与双面信号互连,单元高度可降至5T以下,且供电电阻降低40%,电压稳定性更优。CFET以直接n-p堆叠实现面积减半,但FFET通过双面分离设计提升供电效率和设计灵活性,在超高密度场景(如1纳米以下)更具扩展性。

吴恒研究员也特别指出,Flip FET并不是一种器件结构技术,而是器件三维集成的新架构。其不仅适用于Fin结构的堆叠,还适用于下一代GAA纳米片,具有很强的拓展性。

更加值得关注的是,FFET还充分结合了中国大陆当前的设备情况,可以兼容现有产线,采用非EUV依赖工艺。据业内人士透露,其可在7nm工艺上进行,利用成熟设备,有效降低了产业化的门槛。这种集成思路可以依赖现有光刻技术和设计能力将集成电路的集成度持续提升,更适应中国本土产业链现状。

中国方案的机遇与考验

可以说,Flip FET 的发布,打破了中国在先进逻辑器件领域长期“跟跑”的被动局面,在全球半导体科研领域发出了自己的声音。这也引发台积电、英特尔等巨头的高度关注。台积电研发总监指出,该技术“重新定义了三维集成的技术边界”。

有中国台湾地区业者表示,Flip FET充分利用晶圆背部进行晶体管级三维堆叠,融合了晶圆背部互连和堆叠晶体管集成方法,能提升芯片集成密度和电路设计灵活度。通过创新方案实现类似CFET的PPA,展现了中国大陆业者的研发韧性。

当然,FlipFET面临的挑战还有很多,例如,FlipFET晶圆需要进行减薄工艺和多个背面工艺流程,更容易受到晶圆翘曲和套刻误差的影响,从而降低良率,增加成本。此外,晶圆翻转后,细间距触点和金属的对准也是一个问题。目前的Flip FET还处于研发阶段,未来实现量产仍需面临诸多挑战。

在摩尔定律放缓的背景下,半导体行业面临技术瓶颈。如何持续优化芯片的性能(Performance)、功耗(Power)和面积(Area),已成为全球产业界与学术界共同攻坚的核心命题。Flip FET通过引入双面有源区与双面互连等创新设计,将晶圆集成从传统的单面加工推向三维立体化,为突破摩尔定律桎梏提供了全新范式。相信未来会有更多中国方案被提出。